35-278 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

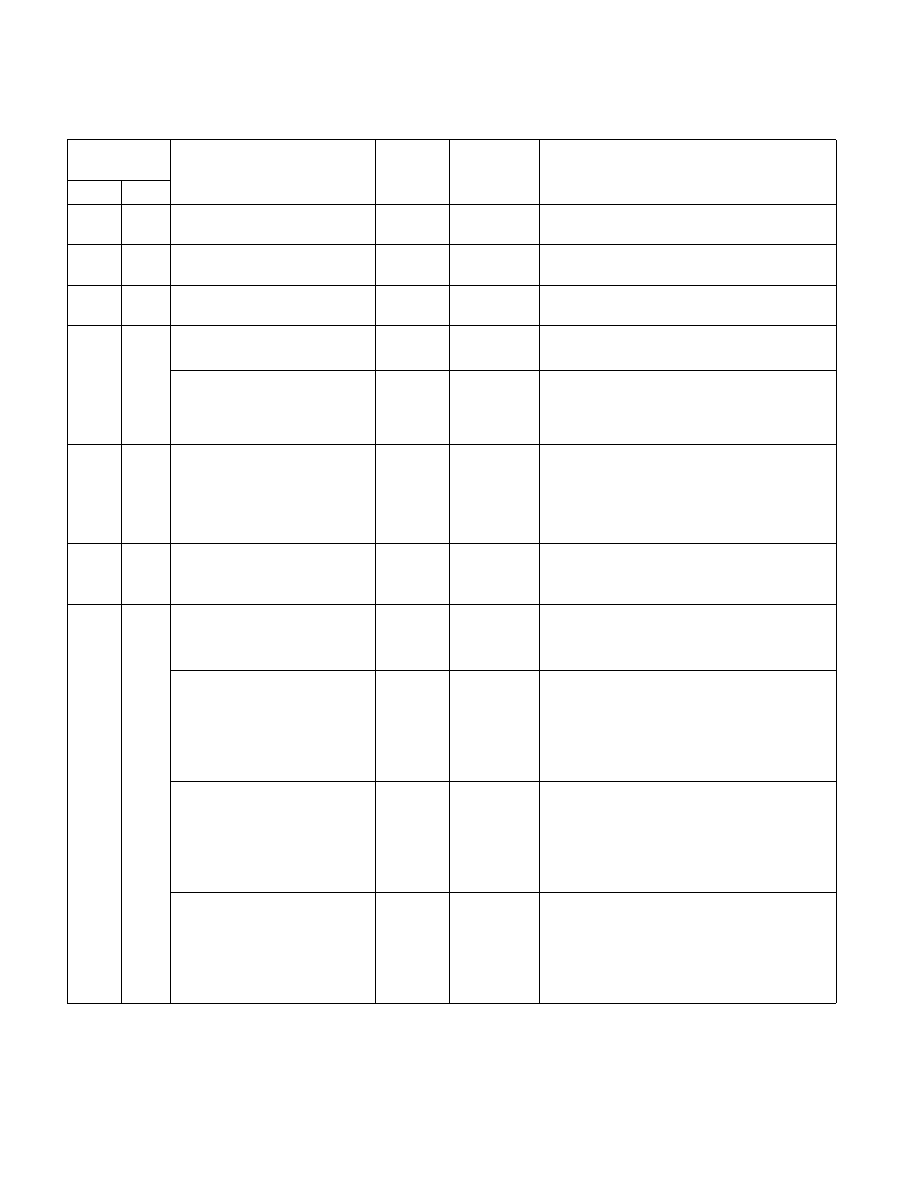

Table 35-41. MSRs in the Pentium® 4 and Intel® Xeon® Processors

Register

Address

Register Name

Fields and Flags

Model

Avail-

ability

Shared/

Unique

1

Bit Description

Hex

Dec

0H

0

IA32_P5_MC_ADDR

0, 1, 2, 3,

4, 6

Shared

See Section 35.22, “MSRs in Pentium Processors.”

1H

1

IA32_P5_MC_TYPE

0, 1, 2, 3,

4, 6

Shared

See Section 35.22, “MSRs in Pentium Processors.”

6H

6

IA32_MONITOR_FILTER_LINE_

SIZE

3, 4, 6

Shared

See Section 8.10.5, “Monitor/Mwait Address

10H

16

IA32_TIME_STAMP_COUNTER

0, 1, 2, 3,

4, 6

Unique

Time Stamp Counter

See Table 35-2.

On earlier processors, only the lower 32 bits are

writable. On any write to the lower 32 bits, the

upper 32 bits are cleared. For processor family

0FH, models 3 and 4: all 64 bits are writable.

17H

23

IA32_PLATFORM_ID

0, 1, 2, 3,

4, 6

Shared

Platform ID (R)

See Table 35-2.

The operating system can use this MSR to

determine “slot” information for the processor and

the proper microcode update to load.

1BH

27

IA32_APIC_BASE

0, 1, 2, 3,

4, 6

Unique

APIC Location and Status (R/W)

See Table 35-2. See Section 10.4.4, “Local APIC

2AH

42

MSR_EBC_HARD_POWERON

0, 1, 2, 3,

4, 6

Shared

Processor Hard Power-On Configuration

(R/W) Enables and disables processor features;

(R) indicates current processor configuration.

0

Output Tri-state Enabled (R)

Indicates whether tri-state output is enabled (1)

or disabled (0) as set by the strapping of SMI#.

The value in this bit is written on the deassertion

of RESET#; the bit is set to 1 when the address

bus signal is asserted.

1

Execute BIST (R)

Indicates whether the execution of the BIST is

enabled (1) or disabled (0) as set by the strapping

of INIT#. The value in this bit is written on the

deassertion of RESET#; the bit is set to 1 when

the address bus signal is asserted.

2

In Order Queue Depth (R)

Indicates whether the in order queue depth for

the system bus is 1 (1) or up to 12 (0) as set by

the strapping of A7#. The value in this bit is

written on the deassertion of RESET#; the bit is

set to 1 when the address bus signal is asserted.