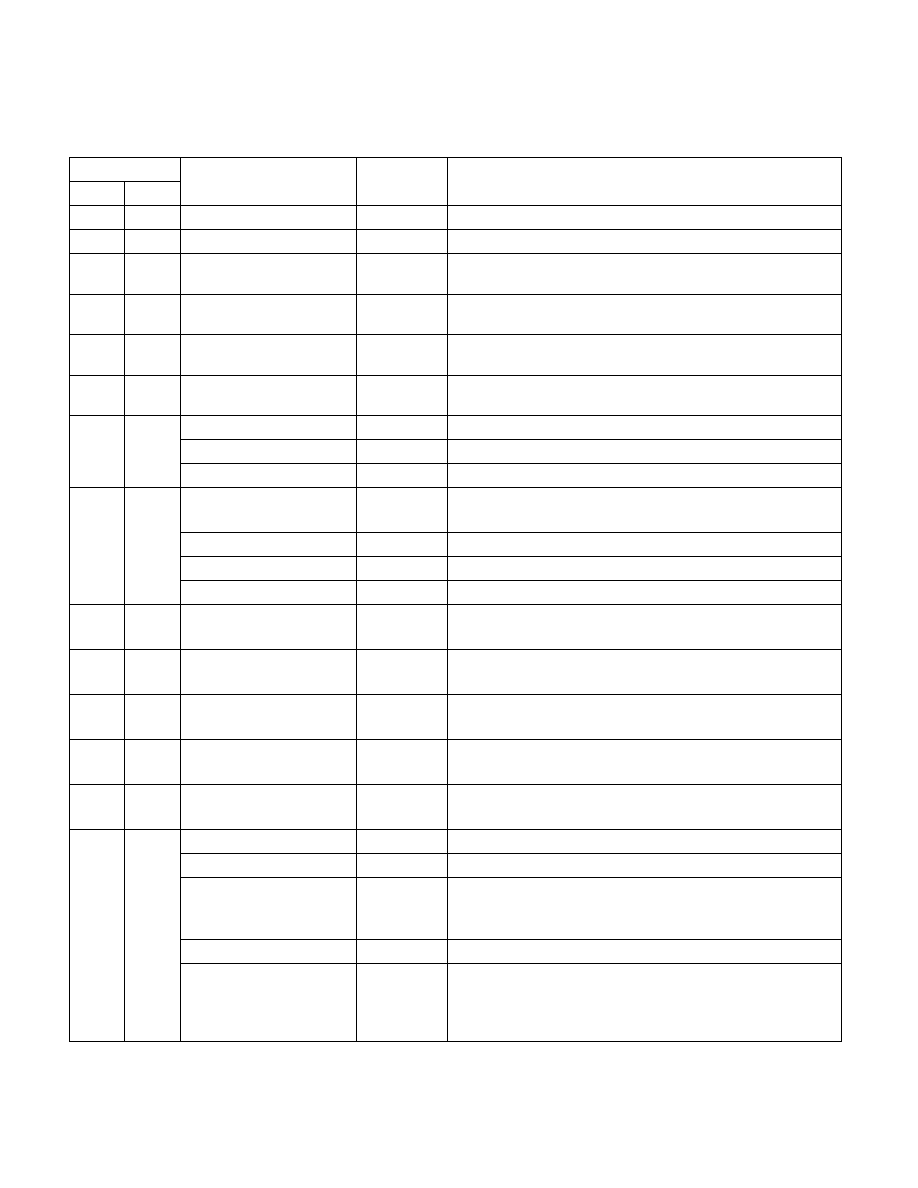

Vol. 3C 35-265

MODEL-SPECIFIC REGISTERS (MSRS)

Table 35-40. Selected MSRs Supported by Intel® Xeon Phi™ Processors with DisplayFamily_DisplayModel Signature

06_57H

Address

Register Name

Scope

Bit Description

Hex

Dec

0H

0

IA32_P5_MC_ADDR

Module

See Section 35.22, “MSRs in Pentium Processors.”

1H

1

IA32_P5_MC_TYPE

Module

See Section 35.22, “MSRs in Pentium Processors.”

6H

6

IA32_MONITOR_FILTER_

SIZE

Thread

See Section 8.10.5, “Monitor/Mwait Address Range Determination.”

10H

16

IA32_TIME_STAMP_

COUNTER

Thread

See Section 17.15, “Time-Stamp Counter,” and see Table 35-2.

17H

23

IA32_PLATFORM_ID

Package

Platform ID (R)

1BH

27

IA32_APIC_BASE

Thread

See Section 10.4.4, “Local APIC Status and Location,” and

34H

52

MSR_SMI_COUNT

Thread

SMI Counter (R/O)

31:0

SMI Count (R/O)

63:32

Reserved.

3AH

58

IA32_FEATURE_CONTROL

Thread

Control Features in Intel 64Processor (R/W)

See Table 35-2.

0

Lock (R/WL)

1

Reserved

2

Enable VMX outside SMX operation (R/WL)

3BH

59

IA32_TSC_ADJUST

THREAD

Per-Logical-Processor TSC ADJUST (R/W)

See Table 35-2.

79H

121

IA32_BIOS_UPDT_TRIG

Core

BIOS Update Trigger Register (W)

See Table 35-2.

8BH

139

IA32_BIOS_SIGN_ID

THREAD

BIOS Update Signature ID (RO)

See Table 35-2.

C1H

193

IA32_PMC0

THREAD

Performance counter register

See Table 35-2.

C2H

194

IA32_PMC1

THREAD

Performance Counter Register

See Table 35-2.

CEH

206

MSR_PLATFORM_INFO

Package

See http://biosbits.org.

7:0

Reserved.

15:8

Package

Maximum Non-Turbo Ratio (R/O)

The is the ratio of the frequency that invariant TSC runs at.

Frequency = ratio * 100 MHz.

27:16

Reserved.

28

Package

Programmable Ratio Limit for Turbo Mode (R/O)

When set to 1, indicates that Programmable Ratio Limits for Turbo

mode is enabled, and when set to 0, indicates Programmable Ratio

Limits for Turbo mode is disabled.