35-262 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

283H

643

IA32_MC3_CTL2

Package

See Table 35-2.

284H

644

IA32_MC4_CTL2

Package

See Table 35-2.

285H

645

IA32_MC5_CTL2

Package

See Table 35-2.

286H

646

IA32_MC6_CTL2

Package

See Table 35-2.

287H

647

IA32_MC7_CTL2

Package

See Table 35-2.

288H

648

IA32_MC8_CTL2

Package

See Table 35-2.

289H

649

IA32_MC9_CTL2

Package

See Table 35-2.

28AH

650

IA32_MC10_CTL2

Package

See Table 35-2.

28BH

651

IA32_MC11_CTL2

Package

See Table 35-2.

28CH

652

IA32_MC12_CTL2

Package

See Table 35-2.

28DH

653

IA32_MC13_CTL2

Package

See Table 35-2.

28EH

654

IA32_MC14_CTL2

Package

See Table 35-2.

28FH

655

IA32_MC15_CTL2

Package

See Table 35-2.

290H

656

IA32_MC16_CTL2

Package

See Table 35-2.

291H

657

IA32_MC17_CTL2

Package

See Table 35-2.

292H

658

IA32_MC18_CTL2

Package

See Table 35-2.

293H

659

IA32_MC19_CTL2

Package

See Table 35-2.

400H

1024

IA32_MC0_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC0 reports MC error from the IFU module.

401H

1025

IA32_MC0_STATUS

Package

402H

1026

IA32_MC0_ADDR

Package

403H

1027

IA32_MC0_MISC

Package

404H

1028

IA32_MC1_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC1 reports MC error from the DCU module.

405H

1029

IA32_MC1_STATUS

Package

406H

1030

IA32_MC1_ADDR

Package

407H

1031

IA32_MC1_MISC

Package

408H

1032

IA32_MC2_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC2 reports MC error from the DTLB module.

409H

1033

IA32_MC2_STATUS

Package

40AH

1034

IA32_MC2_ADDR

Package

40BH

1035

IA32_MC2_MISC

Package

40CH

1036

IA32_MC3_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC3 reports MC error from the MLC module.

40DH

1037

IA32_MC3_STATUS

Package

40EH

1038

IA32_MC3_ADDR

Package

40FH

1039

IA32_MC3_MISC

Package

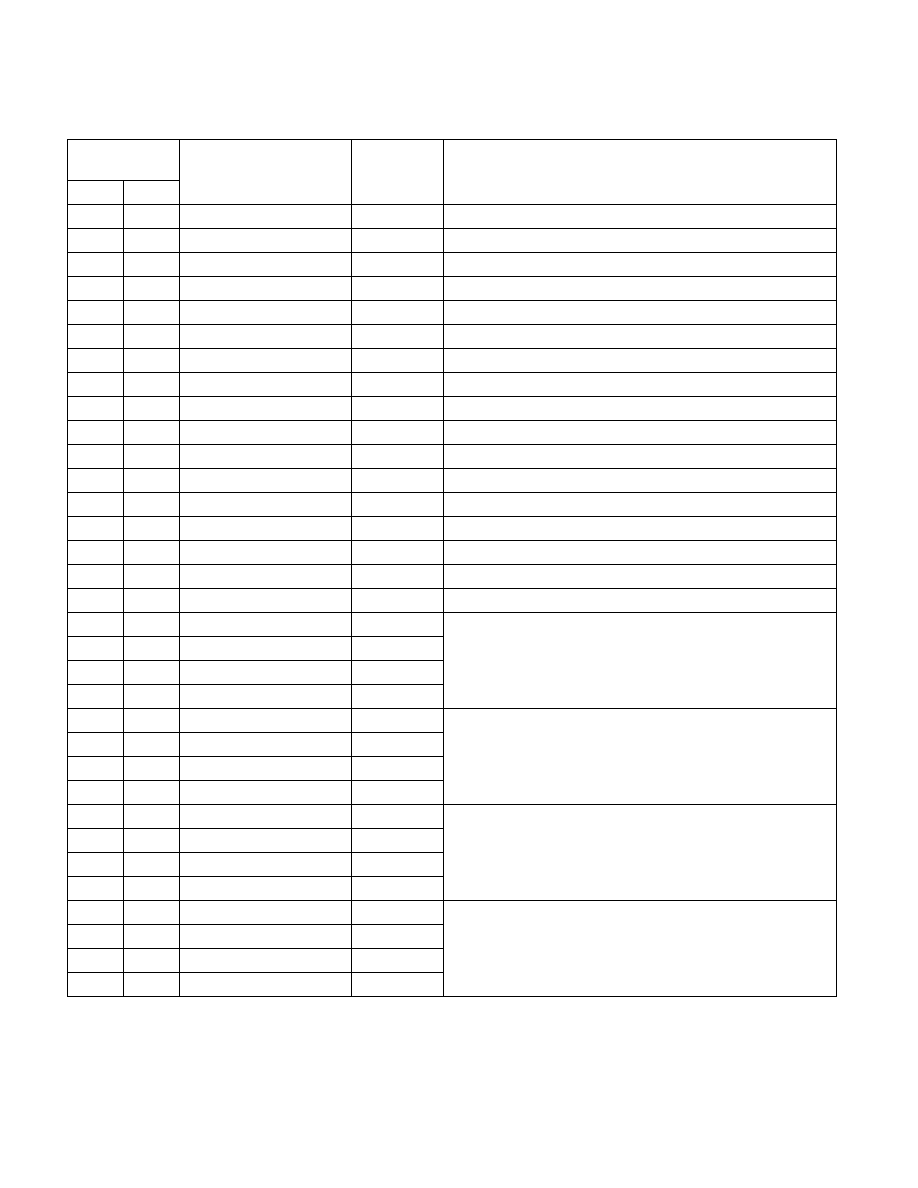

Table 35-39. Machine Check MSRs Supported by Future Intel® Xeon® Processors with DisplayFamily_DisplayModel

06_55H

Register

Address

Register Name

Scope

Bit Description

Hex

Dec