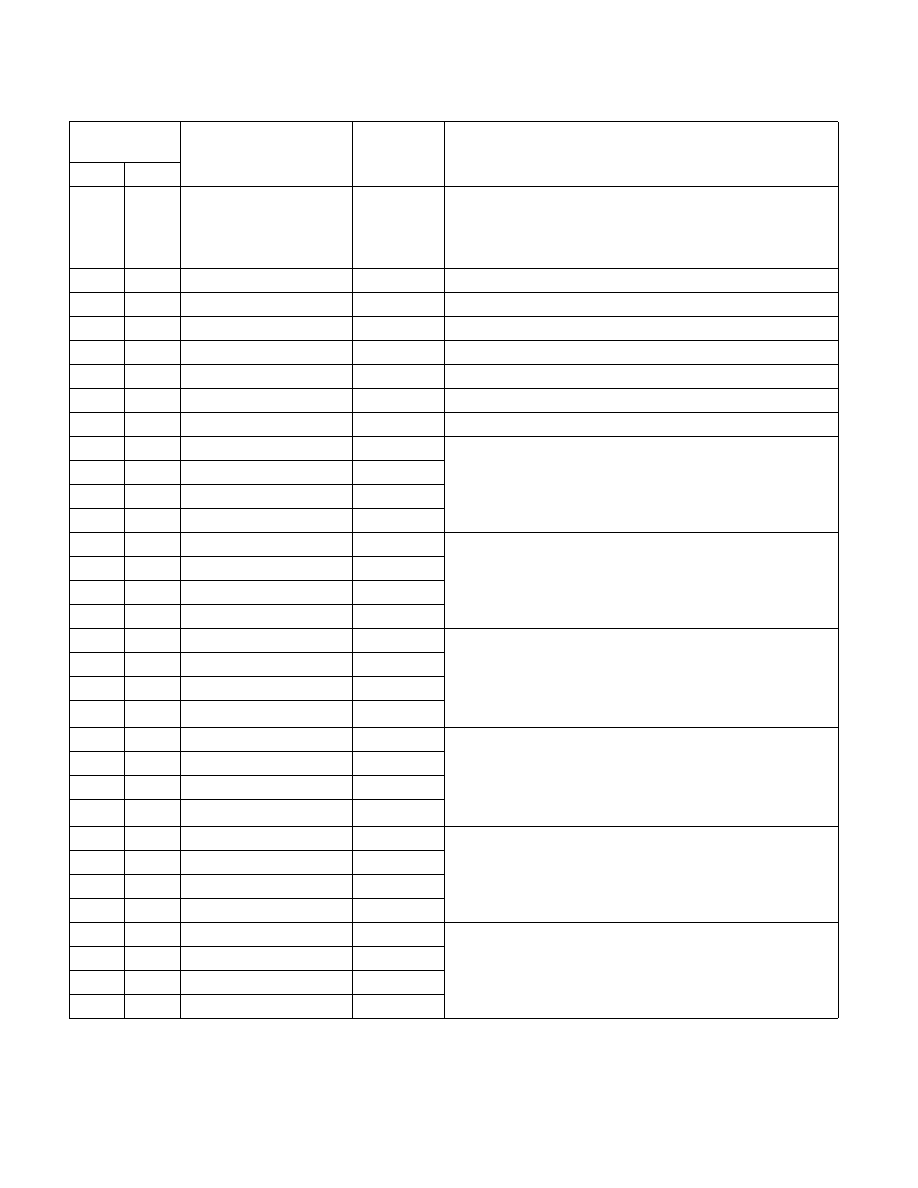

Vol. 3C 35-237

MODEL-SPECIFIC REGISTERS (MSRS)

63

Package

Semaphore for Turbo Ratio Limit Configuration

If 1, the processor uses override configuration

1

specified in

MSR_TURBO_RATIO_LIMIT, MSR_TURBO_RATIO_LIMIT1.

If 0, the processor uses factory-set configuration (Default).

286H

646

IA32_MC6_CTL2

Package

287H

647

IA32_MC7_CTL2

Package

289H

649

IA32_MC9_CTL2

Package

28AH

650

IA32_MC10_CTL2

Package

See Table 35-2.

291H

657

IA32_MC17_CTL2

Package

See Table 35-2.

292H

658

IA32_MC18_CTL2

Package

See Table 35-2.

293H

659

IA32_MC19_CTL2

Package

See Table 35-2.

418H

1048

IA32_MC6_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC6 reports MC error from the integrated I/O module.

419H

1049

IA32_MC6_STATUS

Package

41AH

1050

IA32_MC6_ADDR

Package

41BH

1051

IA32_MC6_MISC

Package

41CH

1052

IA32_MC7_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC7 reports MC error from the home agent HA 0.

41DH

1053

IA32_MC7_STATUS

Package

41EH

1054

IA32_MC7_ADDR

Package

41FH

1055

IA32_MC7_MISC

Package

424H

1060

IA32_MC9_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Banks MC9 through MC 10 report MC error from each channel of

the integrated memory controllers.

425H

1061

IA32_MC9_STATUS

Package

426H

1062

IA32_MC9_ADDR

Package

427H

1063

IA32_MC9_MISC

Package

428H

1064

IA32_MC10_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Banks MC9 through MC 10 report MC error from each channel of

the integrated memory controllers.

429H

1065

IA32_MC10_STATUS

Package

42AH

1066

IA32_MC10_ADDR

Package

42BH

1067

IA32_MC10_MISC

Package

444H

1092

IA32_MC17_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC17 reports MC error from the following pair of CBo/L3

Slices (if the pair is present): CBo0, CBo3, CBo6, CBo9, CBo12,

CBo15.

445H

1093

IA32_MC17_STATUS

Package

446H

1094

IA32_MC17_ADDR

Package

447H

1095

IA32_MC17_MISC

Package

448H

1096

IA32_MC18_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC18 reports MC error from the following pair of CBo/L3

Slices (if the pair is present): CBo1, CBo4, CBo7, CBo10, CBo13,

CBo16.

449H

1097

IA32_MC18_STATUS

Package

44AH

1098

IA32_MC18_ADDR

Package

44BH

1099

IA32_MC18_MISC

Package

Table 35-35. Additional MSRs Supported by Intel® Xeon® Processor D with DisplayFamily_DisplayModel 06_56H

Register

Address

Register Name

Scope

Bit Description

Hex

Dec