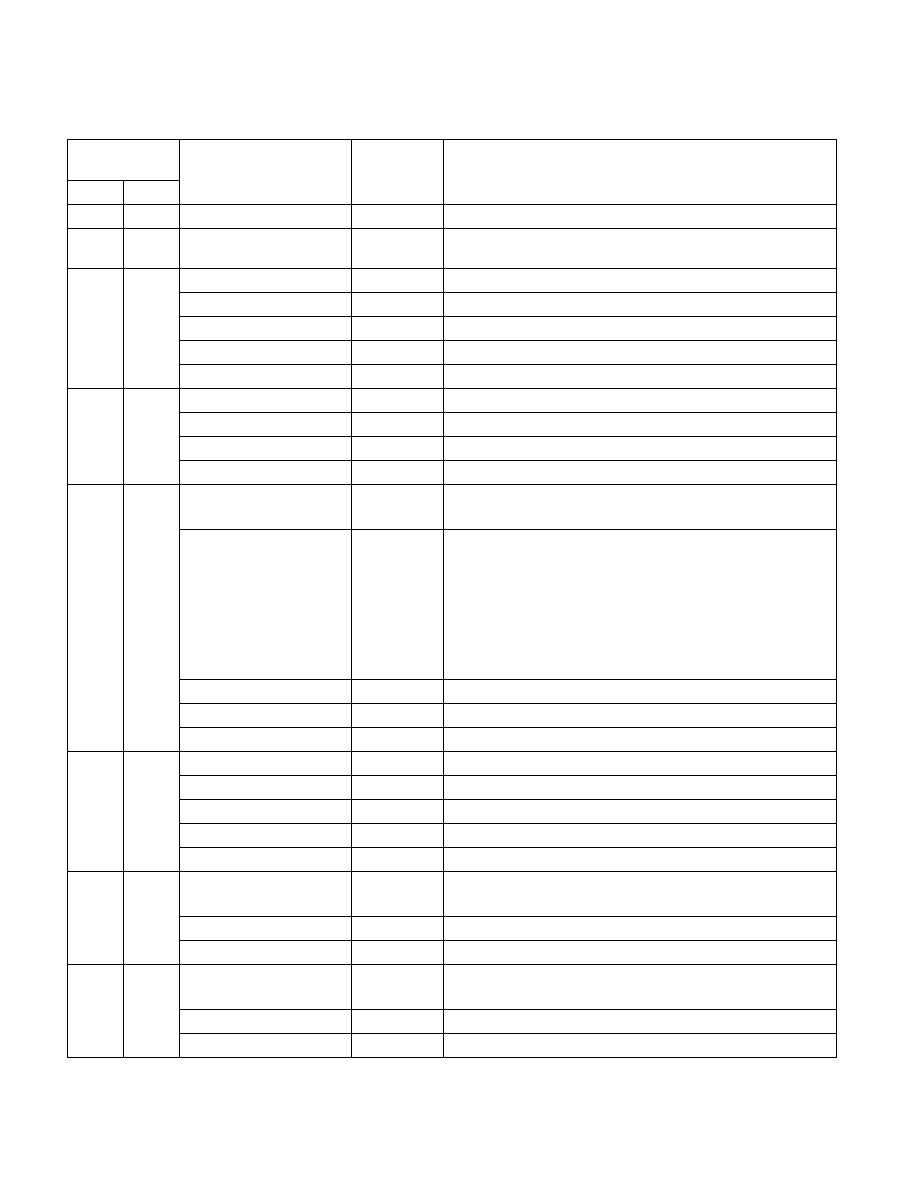

35-234 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

770H

1904

IA32_PM_ENABLE

Package

See Section 14.4.2, “Enabling HWP”

771H

1905

IA32_HWP_CAPABILITIES

Thread

See Section 14.4.3, “HWP Performance Range and Dynamic

774H

1908

IA32_HWP_REQUEST

Thread

See Section 14.4.4, “Managing HWP”

7:0

Minimum Performance (R/W)

15:8

Maximum Performance (R/W)

23:16

Desired Performance (R/W)

63:24

Reserved.

777H

1911

IA32_HWP_STATUS

Thread

See Section 14.4.5, “HWP Feedback”

1:0

Reserved.

2

Excursion to Minimum (RO)

63:3

Reserved.

C8DH

3213

IA32_QM_EVTSEL

THREAD

Monitoring Event Select Register (R/W)

if CPUID.(EAX=07H, ECX=0):EBX.RDT-M[bit 12] = 1

7:0

EventID (RW)

Event encoding:

0x00: no monitoring

0x01: L3 occupancy monitoring

0x02: Total memory bandwidth monitoring

0x03: Local memory bandwidth monitoring

All other encoding reserved

31:8

Reserved.

41:32

RMID (RW)

63:42

Reserved.

C8FH

3215

IA32_PQR_ASSOC

THREAD

Resource Association Register (R/W)

9:0

RMID

31:10

Reserved

51:32

COS (R/W).

63: 52

Reserved

C90H

3216

IA32_L3_QOS_MASK_0

Package

L3 Class Of Service Mask - COS 0 (R/W)

if CPUID.(EAX=10H, ECX=1):EDX.COS_MAX[15:0] >=0

0:19

CBM: Bit vector of available L3 ways for COS 0 enforcement

63:20

Reserved

C91H

3217

IA32_L3_QOS_MASK_1

Package

L3 Class Of Service Mask - COS 1 (R/W)

if CPUID.(EAX=10H, ECX=1):EDX.COS_MAX[15:0] >=1

0:19

CBM: Bit vector of available L3 ways for COS 1 enforcement

63:20

Reserved

Table 35-34. Additional MSRs Common to Intel® Xeon® Processor D and Intel Xeon Processors E5 v4 Family Based

on the Broadwell Microarchitecture

Register

Address

Register Name

Scope

Bit Description

Hex

Dec