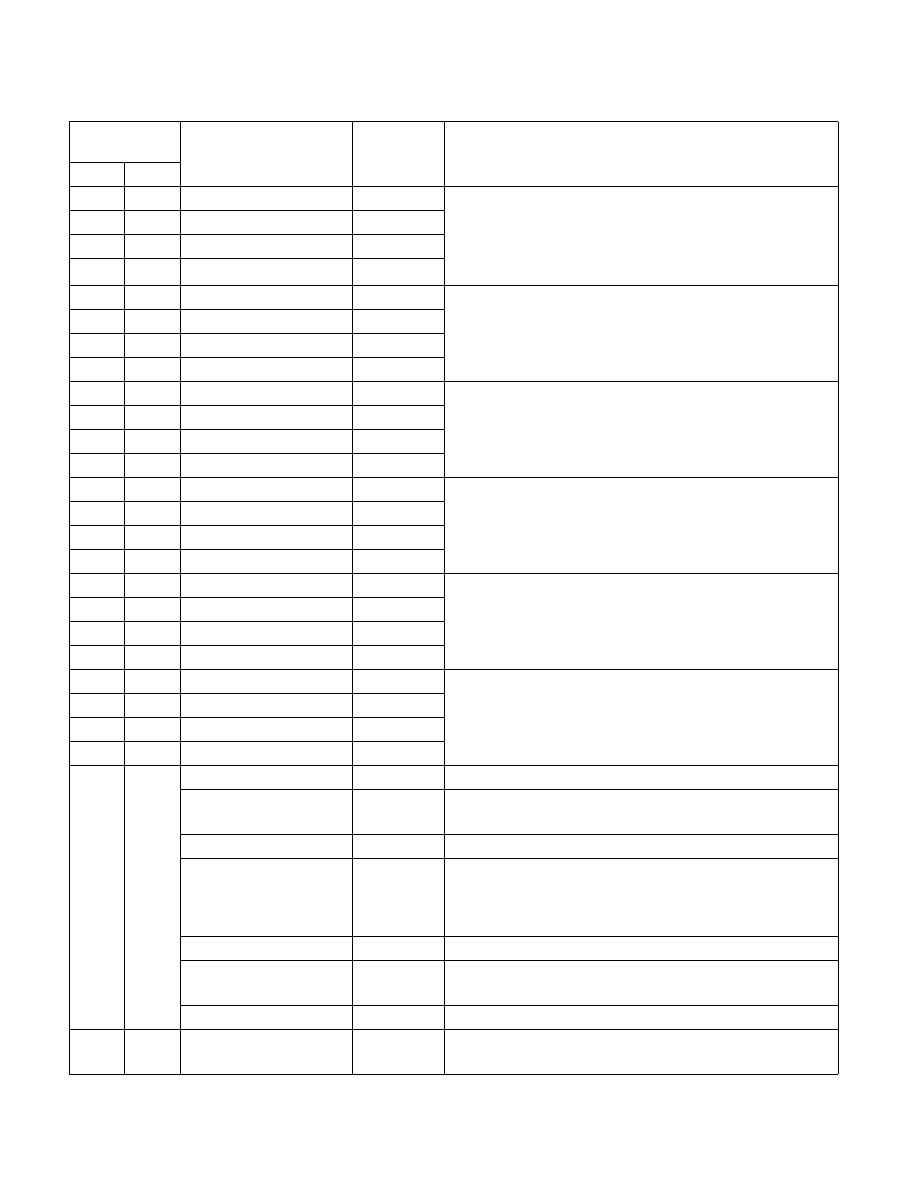

Vol. 3C 35-211

MODEL-SPECIFIC REGISTERS (MSRS)

440H

1088

IA32_MC16_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Banks MC9 through MC 16 report MC error from each channel of

the integrated memory controllers.

441H

1089

IA32_MC16_STATUS

Package

442H

1090

IA32_MC16_ADDR

Package

443H

1091

IA32_MC16_MISC

Package

444H

1092

IA32_MC17_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC17 reports MC error from the following pair of CBo/L3

Slices (if the pair is present): CBo0, CBo3, CBo6, CBo9, CBo12,

CBo15.

445H

1093

IA32_MC17_STATUS

Package

446H

1094

IA32_MC17_ADDR

Package

447H

1095

IA32_MC17_MISC

Package

448H

1096

IA32_MC18_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC18 reports MC error from the following pair of CBo/L3

Slices (if the pair is present): CBo1, CBo4, CBo7, CBo10, CBo13,

CBo16.

449H

1097

IA32_MC18_STATUS

Package

44AH

1098

IA32_MC18_ADDR

Package

44BH

1099

IA32_MC18_MISC

Package

44CH

1100

IA32_MC19_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC19 reports MC error from the following pair of CBo/L3

Slices (if the pair is present): CBo2, CBo5, CBo8, CBo11, CBo14,

CBo17.

44DH

1101

IA32_MC19_STATUS

Package

44EH

1102

IA32_MC19_ADDR

Package

44FH

1103

IA32_MC19_MISC

Package

450H

1104

IA32_MC20_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC20 reports MC error from the Intel QPI 1 module.

451H

1105

IA32_MC20_STATUS

Package

452H

1106

IA32_MC20_ADDR

Package

453H

1107

IA32_MC20_MISC

Package

454H

1108

IA32_MC21_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC21 reports MC error from the Intel QPI 2 module.

455H

1109

IA32_MC21_STATUS

Package

456H

1110

IA32_MC21_ADDR

Package

457H

1111

IA32_MC21_MISC

Package

606H

1542

MSR_RAPL_POWER_UNIT

Package

Unit Multipliers used in RAPL Interfaces (R/O)

3:0

Package

Power Units

See Section 14.9.1, “RAPL Interfaces.”

7:4

Package

Reserved

12:8

Package

Energy Status Units

Energy related information (in Joules) is based on the multiplier,

1/2^ESU; where ESU is an unsigned integer represented by bits

12:8. Default value is 0EH (or 61 micro-joules)

15:13

Package

Reserved

19:16

Package

Time Units

See Section 14.9.1, “RAPL Interfaces.”

63:20

Reserved

618H

1560

MSR_DRAM_POWER_LIMIT

Package

DRAM RAPL Power Limit Control (R/W)

See Section 14.9.5, “DRAM RAPL Domain.”

Table 35-30. Additional MSRs Supported by Intel® Xeon® Processor E5 v3 Family

Register

Address

Register Name

Scope

Bit Description

Hex

Dec