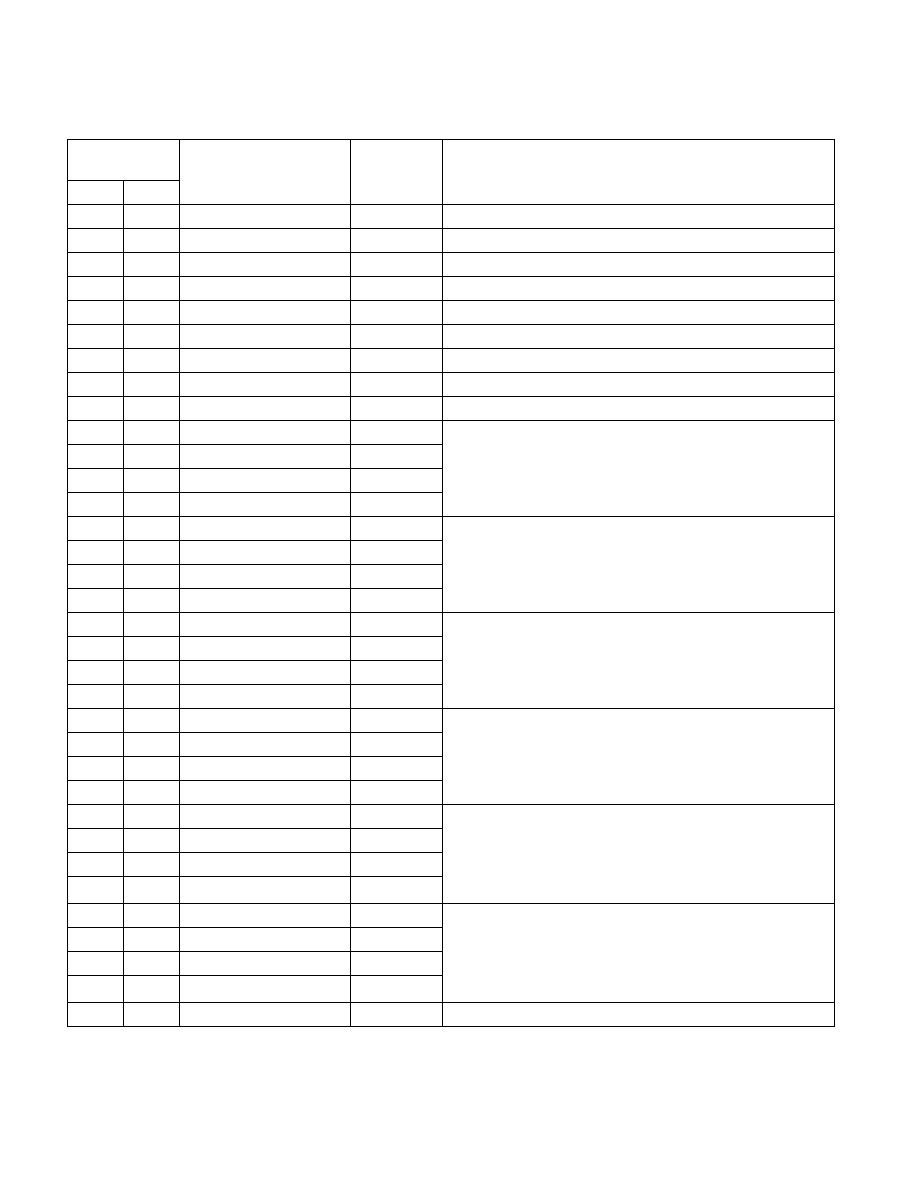

35-180 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

294H

660

IA32_MC20_CTL2

Package

See Table 35-2.

295H

661

IA32_MC21_CTL2

Package

See Table 35-2.

296H

662

IA32_MC22_CTL2

Package

See Table 35-2.

297H

663

IA32_MC23_CTL2

Package

See Table 35-2.

298H

664

IA32_MC24_CTL2

Package

See Table 35-2.

299H

665

IA32_MC25_CTL2

Package

See Table 35-2.

29AH

666

IA32_MC26_CTL2

Package

See Table 35-2.

29BH

667

IA32_MC27_CTL2

Package

See Table 35-2.

29CH

668

IA32_MC28_CTL2

Package

See Table 35-2.

414H

1044

IA32_MC5_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC5 reports MC error from the Intel QPI module.

415H

1045

IA32_MC5_STATUS

Package

416H

1046

IA32_MC5_ADDR

Package

417H

1047

IA32_MC5_MISC

Package

418H

1048

IA32_MC6_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC6 reports MC error from the integrated I/O module.

419H

1049

IA32_MC6_STATUS

Package

41AH

1050

IA32_MC6_ADDR

Package

41BH

1051

IA32_MC6_MISC

Package

41CH

1052

IA32_MC7_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Banks MC7 and MC 8 report MC error from the two home agents.

41DH

1053

IA32_MC7_STATUS

Package

41EH

1054

IA32_MC7_ADDR

Package

41FH

1055

IA32_MC7_MISC

Package

420H

1056

IA32_MC8_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Banks MC7 and MC 8 report MC error from the two home agents.

421H

1057

IA32_MC8_STATUS

Package

422H

1058

IA32_MC8_ADDR

Package

423H

1059

IA32_MC8_MISC

Package

424H

1060

IA32_MC9_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Banks MC9 through MC 16 report MC error from each channel of

the integrated memory controllers.

425H

1061

IA32_MC9_STATUS

Package

426H

1062

IA32_MC9_ADDR

Package

427H

1063

IA32_MC9_MISC

Package

428H

1064

IA32_MC10_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Banks MC9 through MC 16 report MC error from each channel of

the integrated memory controllers.

429H

1065

IA32_MC10_STATUS

Package

42AH

1066

IA32_MC10_ADDR

Package

42BH

1067

IA32_MC10_MISC

Package

42CH

1068

IA32_MC11_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

Table 35-24. MSRs Supported by Intel® Xeon® Processors E5 v2 Product Family (based on Ivy Bridge-E

microarchitecture) (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec