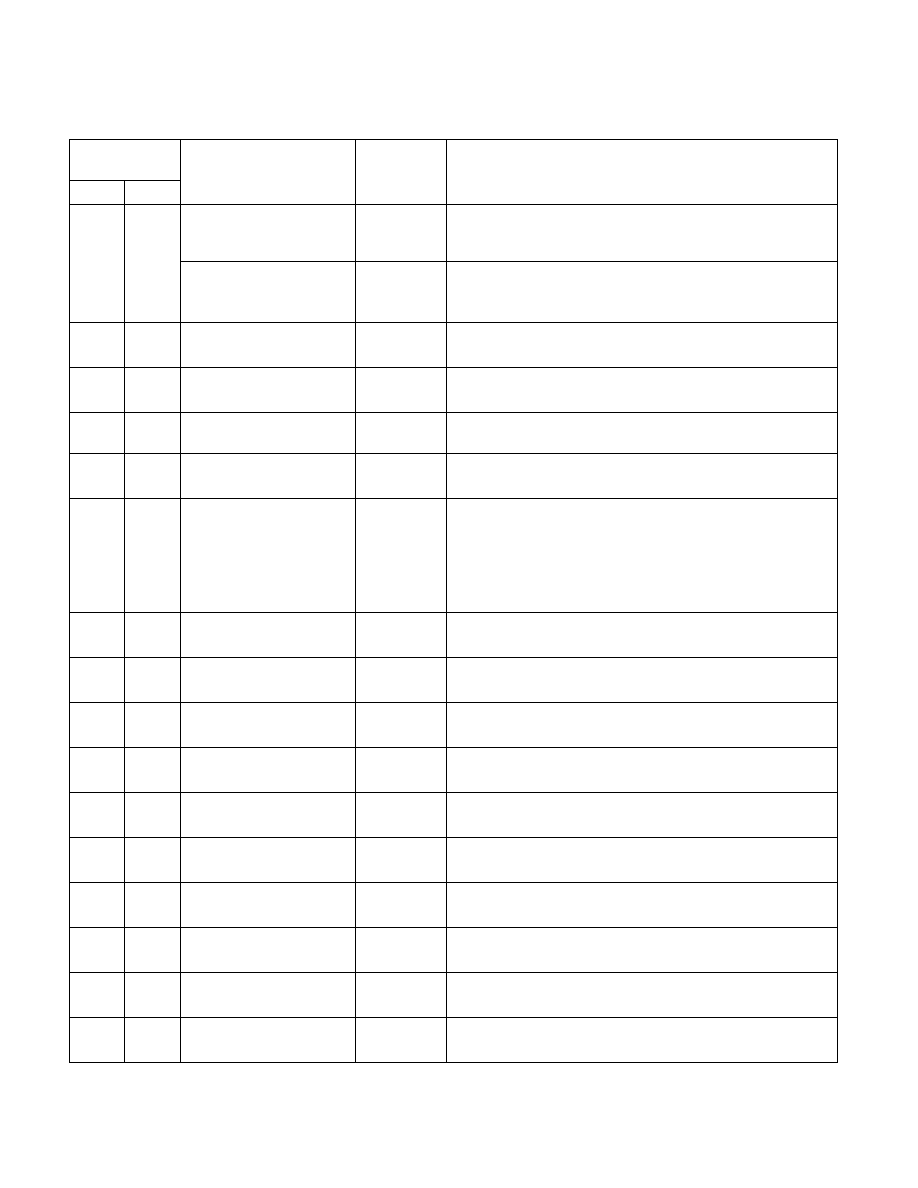

Vol. 3C 35-159

MODEL-SPECIFIC REGISTERS (MSRS)

60DH

1549

MSR_PKG_C2_RESIDENCY

Package

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-

States.

63:0

Package C2 Residency Counter. (R/O)

Value since last reset that this package is in processor-specific C2

states. Count at the same frequency as the TSC.

610H

1552

MSR_PKG_POWER_LIMIT

Package

PKG RAPL Power Limit Control (R/W)

See Section 14.9.3, “Package RAPL Domain.”

611H

1553

MSR_PKG_ENERGY_STATUS Package

PKG Energy Status (R/O)

See Section 14.9.3, “Package RAPL Domain.”

614H

1556

MSR_PKG_POWER_INFO

Package

PKG RAPL Parameters (R/W) See Section 14.9.3, “Package RAPL

638H

1592

MSR_PP0_POWER_LIMIT

Package

PP0 RAPL Power Limit Control (R/W)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

680H

1664

MSR_

LASTBRANCH_0_FROM_IP

Thread

Last Branch Record 0 From IP (R/W)

One of sixteen pairs of last branch record registers on the last

branch record stack. This part of the stack contains pointers to the

source instruction. See also:

• Last Branch Record Stack TOS at 1C9H

• Section 17.7.1 and record format in Section 17.4.8.1

681H

1665

MSR_

LASTBRANCH_1_FROM_IP

Thread

Last Branch Record 1 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

682H

1666

MSR_

LASTBRANCH_2_FROM_IP

Thread

Last Branch Record 2 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

683H

1667

MSR_

LASTBRANCH_3_FROM_IP

Thread

Last Branch Record 3 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

684H

1668

MSR_

LASTBRANCH_4_FROM_IP

Thread

Last Branch Record 4 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

685H

1669

MSR_

LASTBRANCH_5_FROM_IP

Thread

Last Branch Record 5 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

686H

1670

MSR_

LASTBRANCH_6_FROM_IP

Thread

Last Branch Record 6 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

687H

1671

MSR_

LASTBRANCH_7_FROM_IP

Thread

Last Branch Record 7 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

688H

1672

MSR_

LASTBRANCH_8_FROM_IP

Thread

Last Branch Record 8 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

689H

1673

MSR_

LASTBRANCH_9_FROM_IP

Thread

Last Branch Record 9 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

68AH

1674

MSR_

LASTBRANCH_10_FROM_IP

Thread

Last Branch Record 10 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

Table 35-18. MSRs Supported by Intel® Processors

based on Intel® microarchitecture code name Sandy Bridge (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec