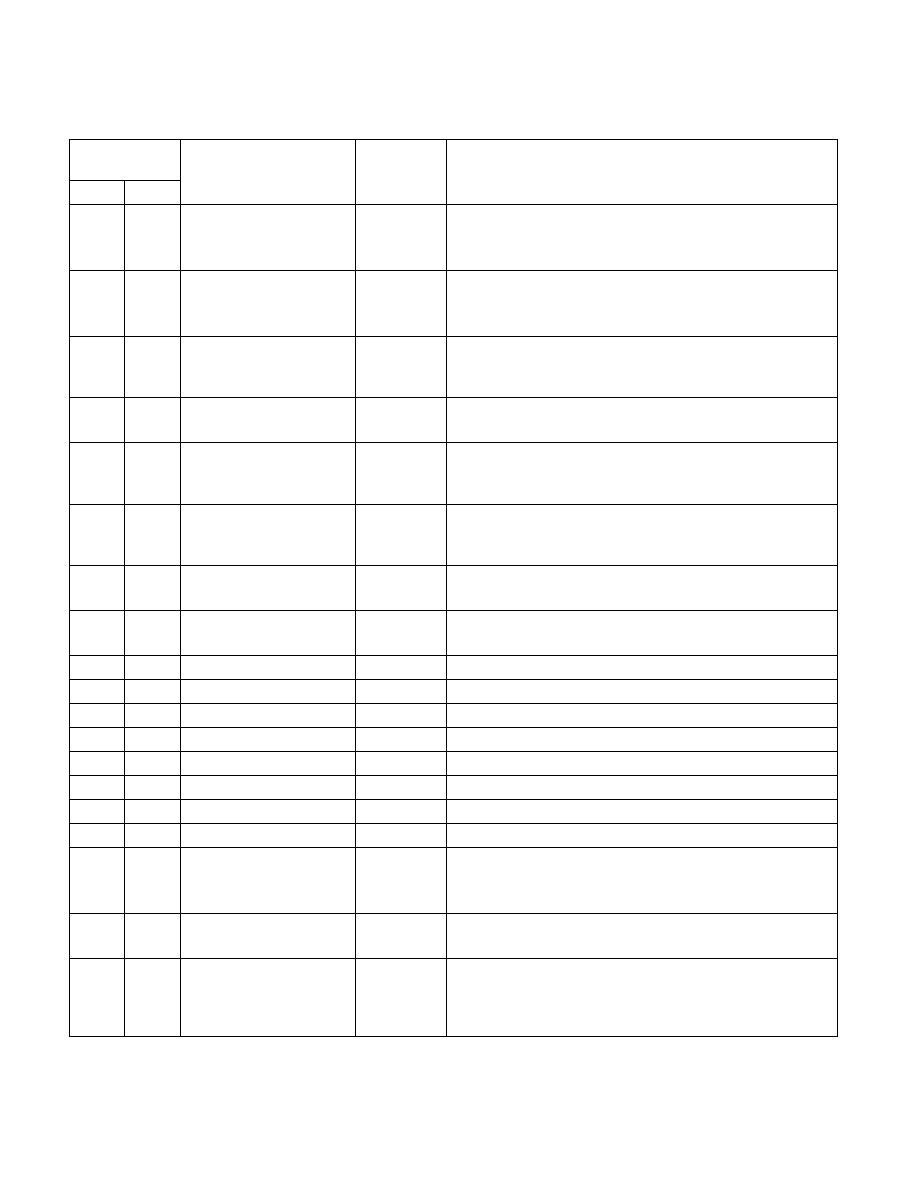

Vol. 3C 35-157

MODEL-SPECIFIC REGISTERS (MSRS)

489H

1161

IA32_VMX_CR4_FIXED1

Thread

Capability Reporting Register of CR4 Bits Fixed to 1 (R/O)

See Table 35-2.

See Appendix A.8, тАЬVMX-Fixed Bits in CR4.тАЭ

48AH

1162

IA32_VMX_VMCS_ENUM

Thread

Capability Reporting Register of VMCS Field Enumeration (R/O)

See Table 35-2.

See Appendix A.9, тАЬVMCS Enumeration.тАЭ

48BH

1163

IA32_VMX_PROCBASED_

CTLS2

Thread

Capability Reporting Register of Secondary Processor-based

VM-execution Controls (R/O)

See Appendix A.3, тАЬVM-Execution Controls.тАЭ

48CH

1164

IA32_VMX_EPT_VPID_ENU

M

Thread

Capability Reporting Register of EPT and VPID (R/O)

See Table 35-2

48DH

1165

IA32_VMX_TRUE_PINBASE

D_CTLS

Thread

Capability Reporting Register of Pin-based VM-execution Flex

Controls (R/O)

See Table 35-2

48EH

1166

IA32_VMX_TRUE_PROCBAS

ED_CTLS

Thread

Capability Reporting Register of Primary Processor-based

VM-execution Flex Controls (R/O)

See Table 35-2

48FH

1167

IA32_VMX_TRUE_EXIT_CTL

S

Thread

Capability Reporting Register of VM-exit Flex Controls (R/O)

See Table 35-2

490H

1168

IA32_VMX_TRUE_ENTRY_C

TLS

Thread

Capability Reporting Register of VM-entry Flex Controls (R/O)

See Table 35-2

4C1H

1217

IA32_A_PMC0

Thread

4C2H

1218

IA32_A_PMC1

Thread

4C3H

1219

IA32_A_PMC2

Thread

4C4H

1220

IA32_A_PMC3

Thread

4C5H

1221

IA32_A_PMC4

Core

4C6H

1222

IA32_A_PMC5

Core

4C7H

1223

IA32_A_PMC6

Core

4C8H

1224

IA32_A_PMC7

Core

600H

1536

IA32_DS_AREA

Thread

DS Save Area (R/W)

See Table 35-2.

See Section 18.12.4, тАЬDebug Store (DS) Mechanism.тАЭ

606H

1542

MSR_RAPL_POWER_UNIT

Package

Unit Multipliers used in RAPL Interfaces (R/O)

See Section 14.9.1, тАЬRAPL Interfaces.тАЭ

60AH

1546

MSR_PKGC3_IRTL

Package

Package C3 Interrupt Response Limit (R/W)

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-

States.

Table 35-18. MSRs Supported by Intel┬о Processors

based on Intel┬о microarchitecture code name Sandy Bridge (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec