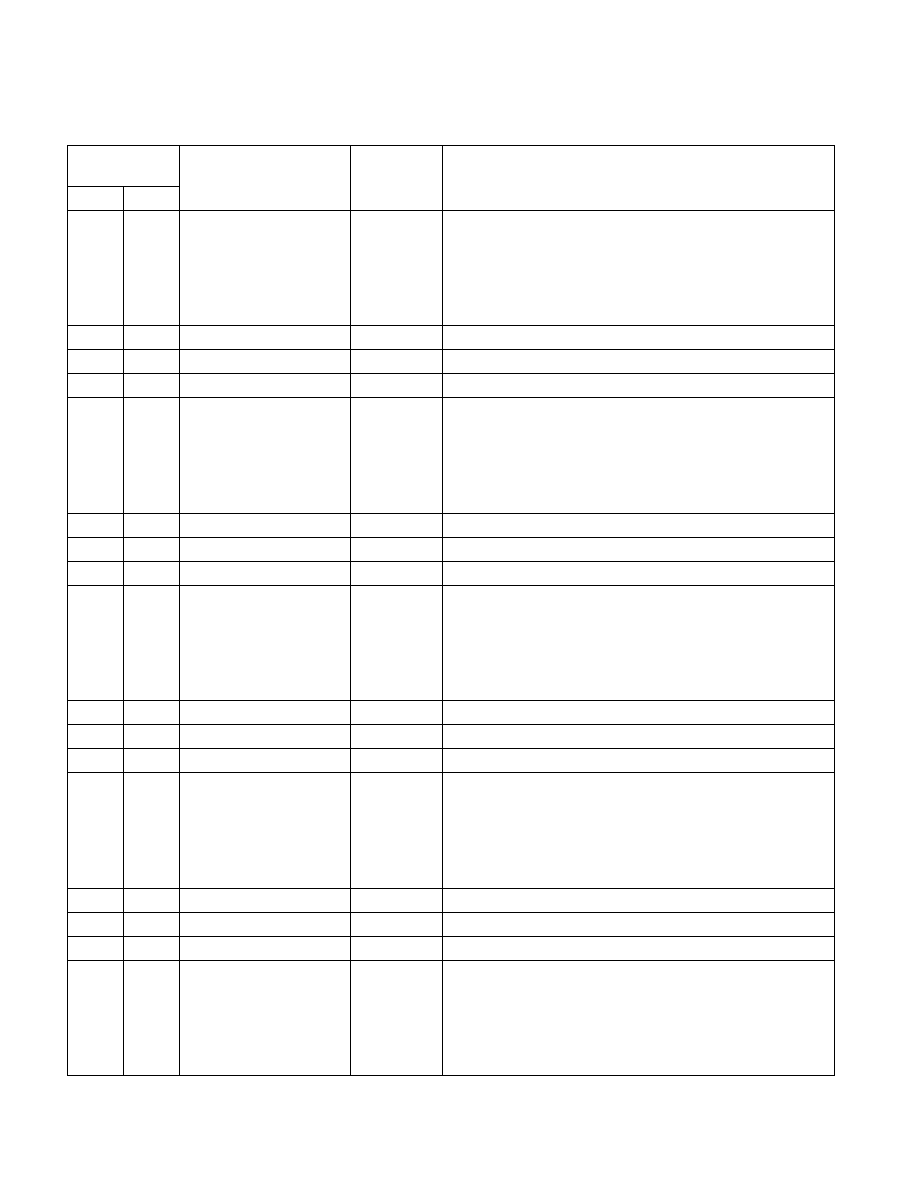

35-118 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

402H

1026

IA32_MC0_ADDR

Package

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

The IA32_MC0_ADDR register is either not implemented or

contains no address if the ADDRV flag in the IA32_MC0_STATUS

register is clear.

When not implemented in the processor, all reads and writes to this

MSR will cause a general-protection exception.

403H

1027

IA32_MC0_MISC

Package

See Section 15.3.2.4, “IA32_MCi_MISC MSRs.”

404H

1028

IA32_MC1_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

405H

1029

IA32_MC1_STATUS

Package

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS.”

406H

1030

IA32_MC1_ADDR

Package

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

The IA32_MC1_ADDR register is either not implemented or

contains no address if the ADDRV flag in the IA32_MC1_STATUS

register is clear.

When not implemented in the processor, all reads and writes to this

MSR will cause a general-protection exception.

407H

1031

IA32_MC1_MISC

Package

See Section 15.3.2.4, “IA32_MCi_MISC MSRs.”

408H

1032

IA32_MC2_CTL

Core

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

409H

1033

IA32_MC2_STATUS

Core

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS.”

40AH

1034

IA32_MC2_ADDR

Core

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

The IA32_MC2_ADDR register is either not implemented or

contains no address if the ADDRV flag in the IA32_MC2_STATUS

register is clear.

When not implemented in the processor, all reads and writes to this

MSR will cause a general-protection exception.

40BH

1035

IA32_MC2_MISC

Core

See Section 15.3.2.4, “IA32_MCi_MISC MSRs.”

40CH

1036

IA32_MC3_CTL

Core

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

40DH

1037

IA32_MC3_STATUS

Core

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS.”

40EH

1038

IA32_MC3_ADDR

Core

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

The MSR_MC4_ADDR register is either not implemented or

contains no address if the ADDRV flag in the MSR_MC4_STATUS

register is clear.

When not implemented in the processor, all reads and writes to this

MSR will cause a general-protection exception.

40FH

1039

IA32_MC3_MISC

Core

See Section 15.3.2.4, “IA32_MCi_MISC MSRs.”

410H

1040

IA32_MC4_CTL

Core

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

411H

1041

IA32_MC4_STATUS

Core

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS.”

412H

1042

IA32_MC4_ADDR

Core

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

The MSR_MC3_ADDR register is either not implemented or

contains no address if the ADDRV flag in the MSR_MC3_STATUS

register is clear.

When not implemented in the processor, all reads and writes to this

MSR will cause a general-protection exception.

Table 35-13. MSRs in Processors Based on Intel® Microarchitecture Code Name Nehalem (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec