Vol. 3C 35-85

MODEL-SPECIFIC REGISTERS (MSRS)

35.5

MSRS IN NEXT GENERATION INTEL ATOM PROCESSORS

Next Generation Intel Atom processors are based on the Goldmont microarchitecture. These processors support

MSRs listed in Table 35-6 and Table 35-12. These processors have a CPUID signature with

DisplayFamily_DisplayModel including 06_5CH; see Table 35-1.

In the Goldmont microarchitecture, the scope column indicates the following: “Core” means each processor core

has a separate MSR, or a bit field not shared with another processor core. “Module” means the MSR or the bit field

is shared by a pair of processor cores in the physical package. “Package” means all processor cores in the physical

package share the same MSR or bit interface.

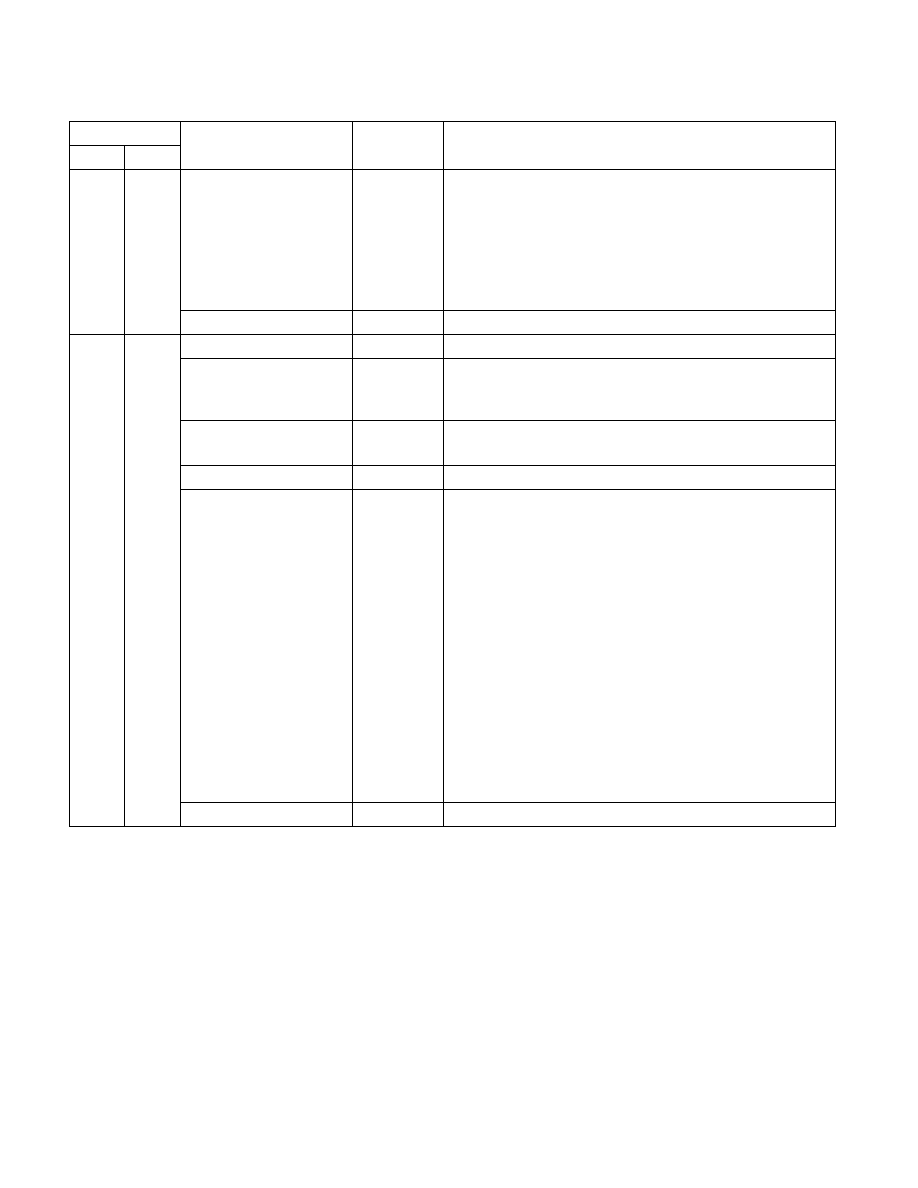

18:16

C-state Range (R/W)

Specifies the encoding value of the maximum C-State code name to

be included when IO read to MWAIT redirection is enabled by

MSR_PKG_CST_CONFIG_CONTROL[bit10]:

000b - C3 is the max C-State to include

001b - Deep Power Down Technology is the max C-State

010b - C7 is the max C-State to include

63:19

Reserved.

638H

1592

MSR_PP0_POWER_LIMIT

Package

PP0 RAPL Power Limit Control (R/W)

14:0

PP0 Power Limit #1. (R/W)

See Section 14.9.4, “PP0/PP1 RAPL Domains.” and

MSR_RAPL_POWER_UNIT in Table 35-8.

15

Enable Power Limit #1. (R/W)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

16

Reserved

23:17

Time Window for Power Limit #1. (R/W)

Specifies the time duration over which the average power must

remain below PP0_POWER_LIMIT #1(14:0). Supported Encodings:

0x0: 1 second time duration.

0x1: 5 second time duration (Default).

0x2: 10 second time duration.

0x3: 15 second time duration.

0x4: 20 second time duration.

0x5: 25 second time duration.

0x6: 30 second time duration.

0x7: 35 second time duration.

0x8: 40 second time duration.

0x9: 45 second time duration.

0xA: 50 second time duration.

0xB-0x7F - reserved.

63:24

Reserved

Table 35-11. MSRs in Intel Atom Processors Based on the Airmont Microarchitecture (Contd.)

Address

Register Name

Scope

Bit Description

Hex

Dec