4-24 Vol. 3A

PAGING

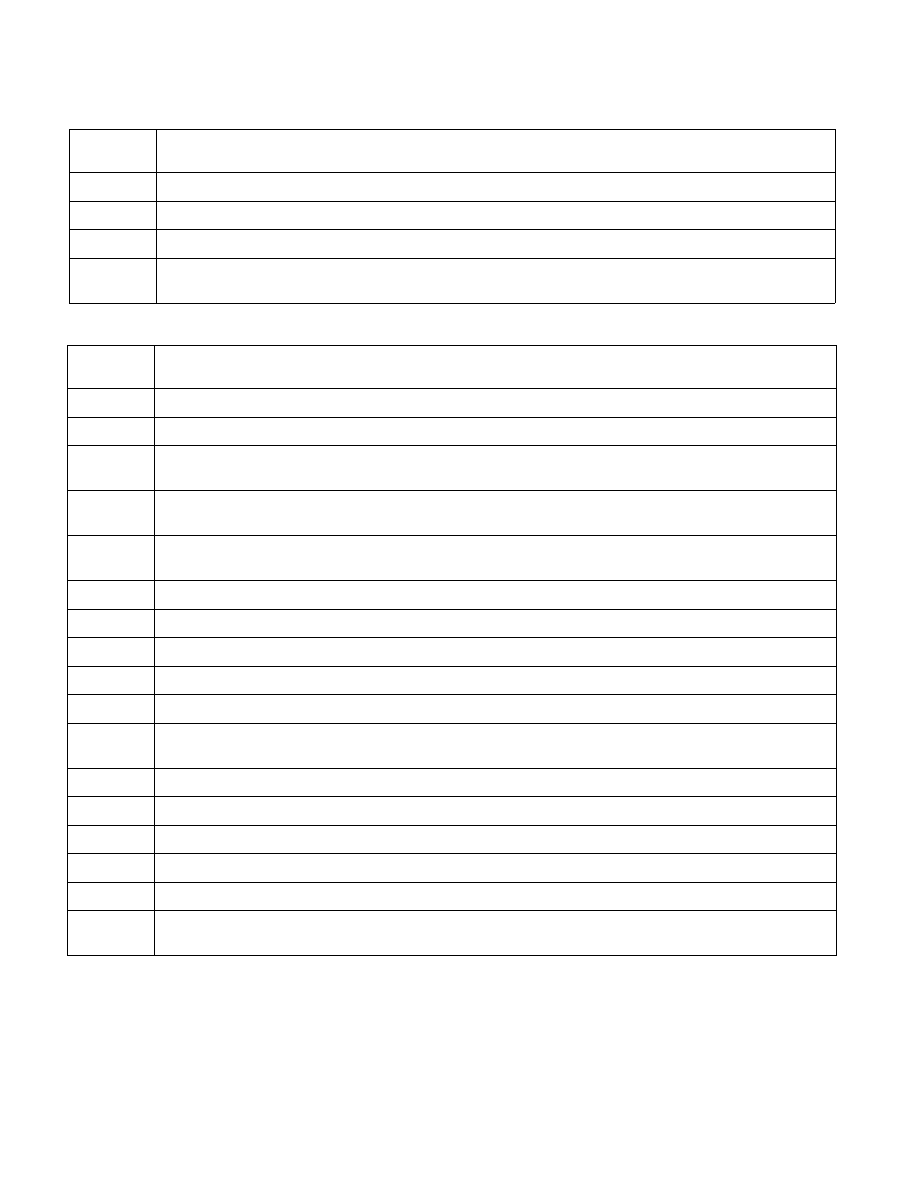

M–1:12

Physical address of 4-KByte aligned page-directory-pointer table referenced by this entry

51:M

Reserved (must be 0)

62:52

Ignored

63 (XD)

If IA32_EFER.NXE = 1, execute-disable (if 1, instruction fetches are not allowed from the 512-GByte region

controlled by this entry; see Section 4.6); otherwise, reserved (must be 0)

Table 4-15. Format of an IA-32e Page-Directory-Pointer-Table Entry (PDPTE) that Maps a 1-GByte Page

Bit

Position(s)

Contents

0 (P)

Present; must be 1 to map a 1-GByte page

1 (R/W)

Read/write; if 0, writes may not be allowed to the 1-GByte page referenced by this entry (see Section 4.6)

2 (U/S)

User/supervisor; if 0, user-mode accesses are not allowed to the 1-GByte page referenced by this entry (see Section

3 (PWT)

Page-level write-through; indirectly determines the memory type used to access the 1-GByte page referenced by this

entry (see Section 4.9.2)

4 (PCD)

Page-level cache disable; indirectly determines the memory type used to access the 1-GByte page referenced by this

entry (see Section 4.9.2)

5 (A)

Accessed; indicates whether software has accessed the 1-GByte page referenced by this entry (see Section 4.8)

6 (D)

Dirty; indicates whether software has written to the 1-GByte page referenced by this entry (see Section 4.8)

7 (PS)

Page size; must be 1 (otherwise, this entry references a page directory; see Table 4-16)

8 (G)

Global; if CR4.PGE = 1, determines whether the translation is global (see Section 4.10); ignored otherwise

11:9

Ignored

12 (PAT)

Indirectly determines the memory type used to access the 1-GByte page referenced by this entry (see Section

1

29:13

Reserved (must be 0)

(M–1):30

Physical address of the 1-GByte page referenced by this entry

51:M

Reserved (must be 0)

58:52

Ignored

62:59

Protection key; if CR4.PKE = 1, determines the protection key of the page (see Section 4.6.2); ignored otherwise

63 (XD)

If IA32_EFER.NXE = 1, execute-disable (if 1, instruction fetches are not allowed from the 1-GByte page controlled by

this entry; see Section 4.6); otherwise, reserved (must be 0)

NOTES:

1. The PAT is supported on all processors that support IA-32e paging.

Table 4-14. Format of an IA-32e PML4 Entry (PML4E) that References a Page-Directory-Pointer Table (Contd.)

Bit

Position(s)

Contents