Vol. 3C 29-13

APIC VIRTUALIZATION AND VIRTUAL INTERRUPTS

•

If the value is non-zero, the logical processor performs self-IPI virtualization with the 8-bit vector in

EAX[7:0] (see Section 29.1.5).

•

If the value is zero, the logical processor causes an APIC-write VM exit as if there had been a write

access to page offset 3F0H on the APIC-access page (see Section 29.4.3.3).

If special processing does not apply, the instruction operates normally. If the local APIC is in x2APIC mode

and ECX indicates a writable APIC register, the value in EDX:EAX is written to that register. If the local APIC is

not in x2APIC mode or ECX does not indicate a writable APIC register, a general-protection fault occurs.

29.6 POSTED-INTERRUPT

PROCESSING

Posted-interrupt processing is a feature by which a processor processes the virtual interrupts by recording them as

pending on the virtual-APIC page.

Posted-interrupt processing is enabled by setting the “process posted interrupts” VM-execution control. The

processing is performed in response to the arrival of an interrupt with the posted-interrupt notification vector.

In response to such an interrupt, the processor processes virtual interrupts recorded in a data structure called a

posted-interrupt descriptor. The posted-interrupt notification vector and the address of the posted-interrupt

descriptor are fields in the VMCS; see Section 24.6.8.

If the “process posted interrupts” VM-execution control is 1, a logical processor uses a 64-byte posted-interrupt

descriptor located at the posted-interrupt descriptor address. The posted-interrupt descriptor has the following

format:

The notation PIR (posted-interrupt requests) refers to the 256 posted-interrupt bits in the posted-interrupt

descriptor.

Use of the posted-interrupt descriptor differs from that of other data structures that are referenced by pointers in

a VMCS. There is a general requirement that software ensure that each such data structure is modified only when

no logical processor with a current VMCS that references it is in VMX non-root operation. That requirement does

not apply to the posted-interrupt descriptor. There is a requirement, however, that such modifications be done

using locked read-modify-write instructions.

If the “external-interrupt exiting” VM-execution control is 1, any unmasked external interrupt causes a VM exit

(see Section 25.2). If the “process posted interrupts” VM-execution control is also 1, this behavior is changed and

the processor handles an external interrupt as follows:

14

1. The local APIC is acknowledged; this provides the processor core with an interrupt vector, called here the

physical vector.

2. If the physical vector equals the posted-interrupt notification vector, the logical processor continues to the next

step. Otherwise, a VM exit occurs as it would normally due to an external interrupt; the vector is saved in the

VM-exit interruption-information field.

3. The processor clears the outstanding-notification bit in the posted-interrupt descriptor. This is done atomically

so as to leave the remainder of the descriptor unmodified (e.g., with a locked AND operation).

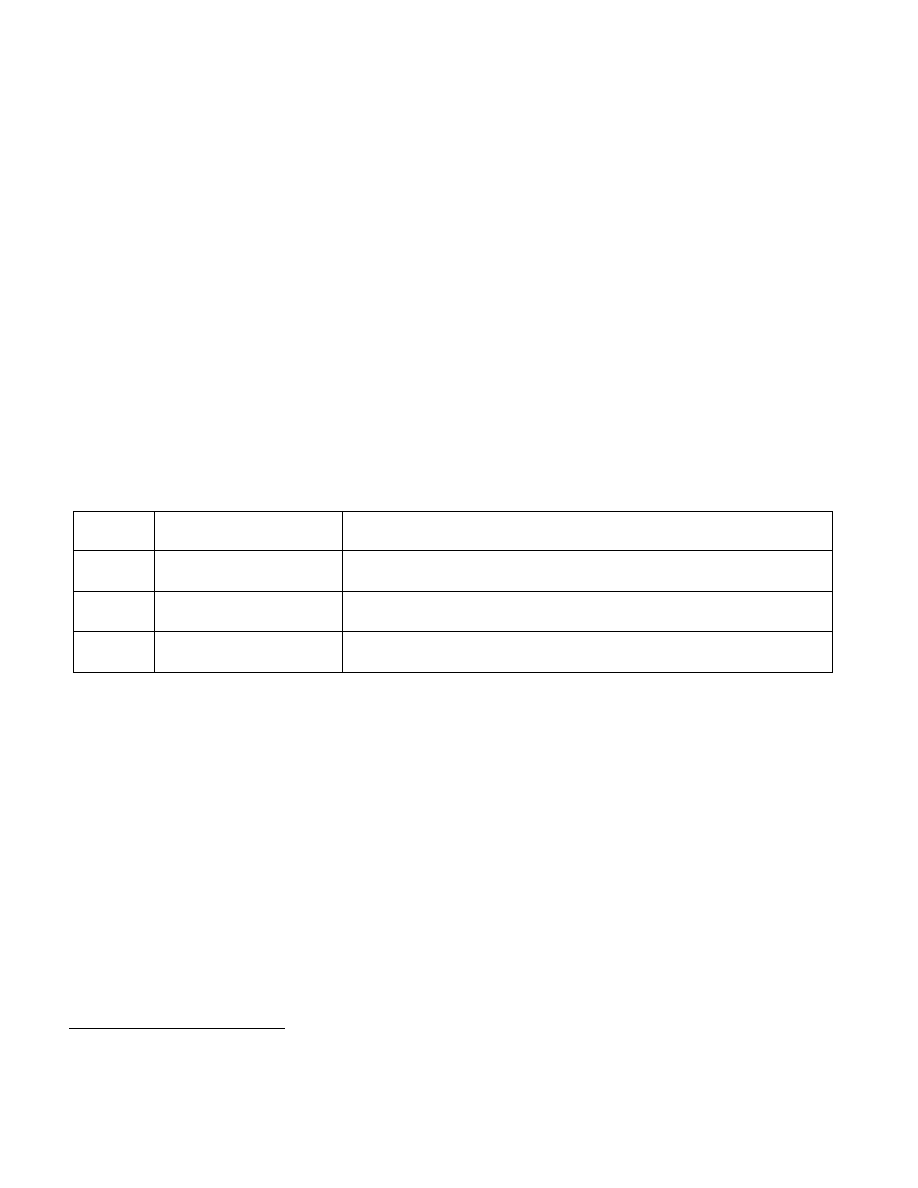

Table 29-1. Format of Posted-Interrupt Descriptor

Bit

Position(s)

Name

Description

255:0

Posted-interrupt requests

One bit for each interrupt vector. There is a posted-interrupt request for a vector if

the corresponding bit is 1

256

Outstanding notification

If this bit is set, there is a notification outstanding for one or more posted interrupts

in bits 255:0

511:257

Reserved for software and

other agents

These bits may be used by software and by other agents in the system (e.g.,

chipset). The processor does not modify these bits.

14. VM entry ensures that the “process posted interrupts” VM-execution control is 1 only if the “external-interrupt exiting” VM-execu-

tion control is also 1. SeeSection 26.2.1.1.