Vol. 3C 27-7

VM EXITS

•

For an APIC-access VM exit caused by the MASKMOVQ instruction or the MASKMOVDQU instruction, the

access type is “data write during instruction execution.”

•

For an APIC-access VM exit caused by the MONITOR instruction, the access type is “data read during

instruction execution.”

Such a VM exit stores 1 for bit 31 for IDT-vectoring information field (see Section 27.2.3) if and only if it

sets bits 15:12 of the exit qualification to 0011b (linear access during event delivery) or 1010b (guest-

physical access during event delivery).

See Section 29.4.4 for further discussion of these instructions and APIC-access VM exits.

For APIC-access VM exits resulting from physical accesses to the APIC-access page (see Section 29.4.6),

the exit qualification is undefined.

— For an EPT violation, the exit qualification contains information about the access causing the EPT violation

and has the format given in Table 27-7.

An EPT violation that occurs during as a result of execution of a read-modify-write operation sets bit 1 (data

write). Whether it also sets bit 0 (data read) is implementation-specific and, for a given implementation,

may differ for different kinds of read-modify-write operations.

31:16

For LMSW, the LMSW source data

For CLTS and MOV CR, cleared to 0

63:32

Reserved (cleared to 0). These bits exist only on processors that support Intel 64 architecture.

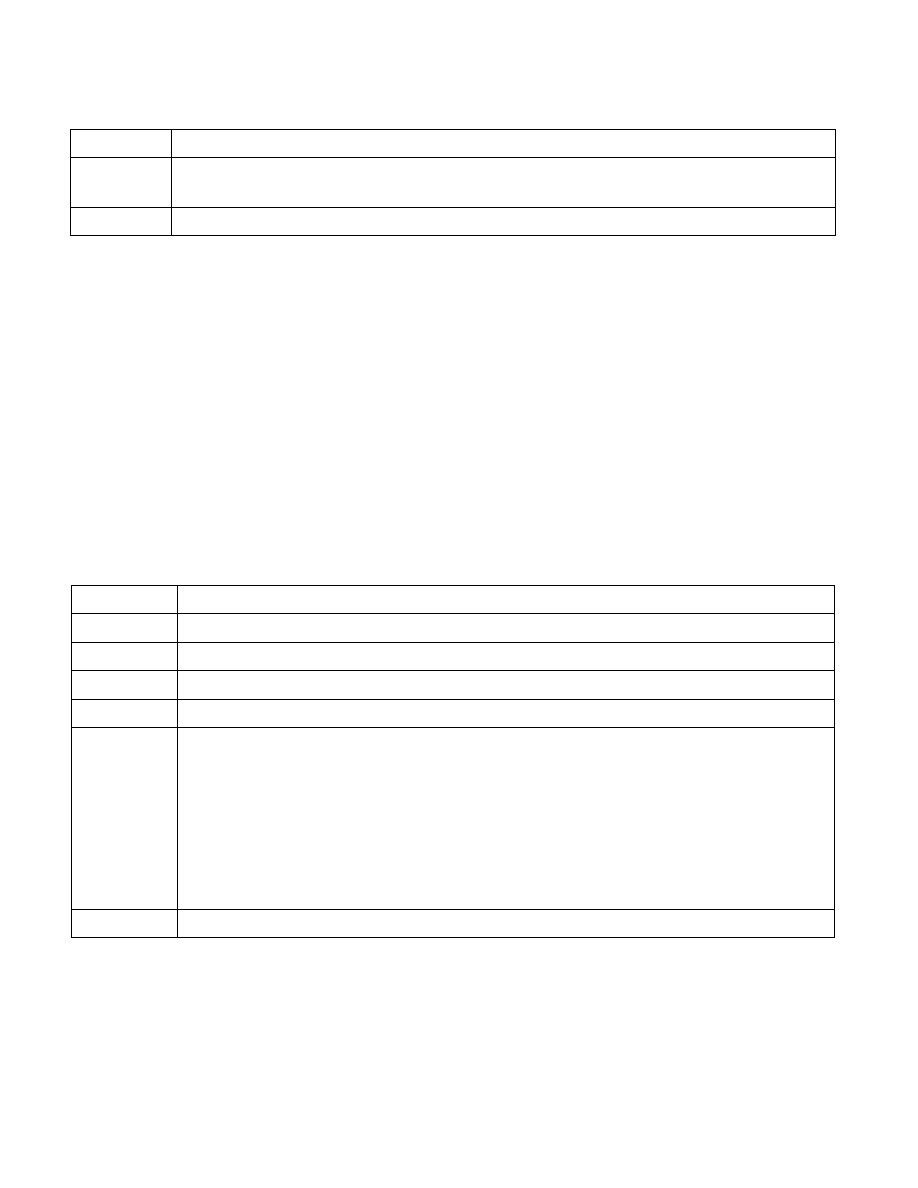

Table 27-4. Exit Qualification for MOV DR

Bit Position(s)

Contents

2:0

Number of debug register

3

Reserved (cleared to 0)

4

Direction of access (0

=

MOV to DR; 1

=

MOV from DR)

7:5

Reserved (cleared to 0)

11:8

General-purpose register:

0 = RAX

1 = RCX

2 = RDX

3 = RBX

4 = RSP

5 = RBP

6 = RSI

7 = RDI

8 –15 = R8 – R15, respectively

63:12

Reserved (cleared to 0)

Table 27-3. Exit Qualification for Control-Register Accesses (Contd.)

Bit Positions

Contents