24-16 Vol. 3C

VIRTUAL MACHINE CONTROL STRUCTURES

24.6.14 VM-Function

Controls

The VM-function controls constitute a 64-bit vector that governs use of the VMFUNC instruction in VMX non-root

operation. This field is supported only on processors that support the 1-settings of both the “activate secondary

controls” primary processor-based VM-execution control and the “enable VM functions” secondary processor-

based VM-execution control.

Table 24-9 lists the VM-function controls. See Section 25.5.5 for more details of how these controls affect processor

behavior in VMX non-root operation.

All other bits in this field are reserved to 0. Software should consult the VMX capability MSR IA32_VMX_VMFUNC

(see Appendix A.11) to determine which bits are reserved. Failure to clear reserved bits causes subsequent

VM entries to fail (see Section 26.2.1.1).

Processors that support the 1-setting of the “EPTP switching” VM-function control also support a 64-bit field called

the EPTP-list address. This field contains the physical address of the 4-KByte EPTP list. The EPTP list comprises

512 8-Byte entries (each an EPTP value) and is used by the EPTP-switching VM function (see Section 25.5.5.3).

24.6.15 VMCS Shadowing Bitmap Addresses

On processors that support the 1-setting of the “VMCS shadowing” VM-execution control, the VM-execution control

fields include the 64-bit physical addresses of the VMREAD bitmap and the VMWRITE bitmap. Each bitmap is 4

KBytes in size and thus contains 32 KBits. The addresses are the VMREAD-bitmap address and the VMWRITE-

bitmap address.

If the “VMCS shadowing” VM-execution control is 1, executions of VMREAD and VMWRITE may consult these

bitmaps (see Section 24.10 and Section 30.3).

24.6.16 ENCLS-Exiting

Bitmap

The ENCLS-exiting bitmap is a 64-bit field. If the “enable ENCLS exiting” VM-execution control is 1, execution of

ENCLS causes a VM exit if the bit in this field corresponding to the value of EAX is 1. If the bit is 0, the instruction

executes normally. See Section 25.1.3 for more information.

24.6.17 Control Field for Page-Modification Logging

The PML address is a 64-bit field. It is the 4-KByte aligned address of the page-modification log. The page-

modification log consists of 512 64-bit entries. It is used for the page-modification logging feature. Details of the

page-modification logging are given in Section 28.2.5.

If the “enable PML” VM-execution control is 1, VM entry ensures that the PML address is 4-KByte aligned. The PML

address exists only on processors that support the 1-setting of the “enable PML” VM-execution control.

24.6.18 Controls for Virtualization Exceptions

On processors that support the 1-setting of the “EPT-violation #VE” VM-execution control, the VM-execution

control fields include the following:

•

Virtualization-exception information address (64 bits). This field contains the physical address of the

virtualization-exception information area. When a logical processor encounters a virtualization exception,

it saves virtualization-exception information at the virtualization-exception information address; see Section

25.5.6.2.

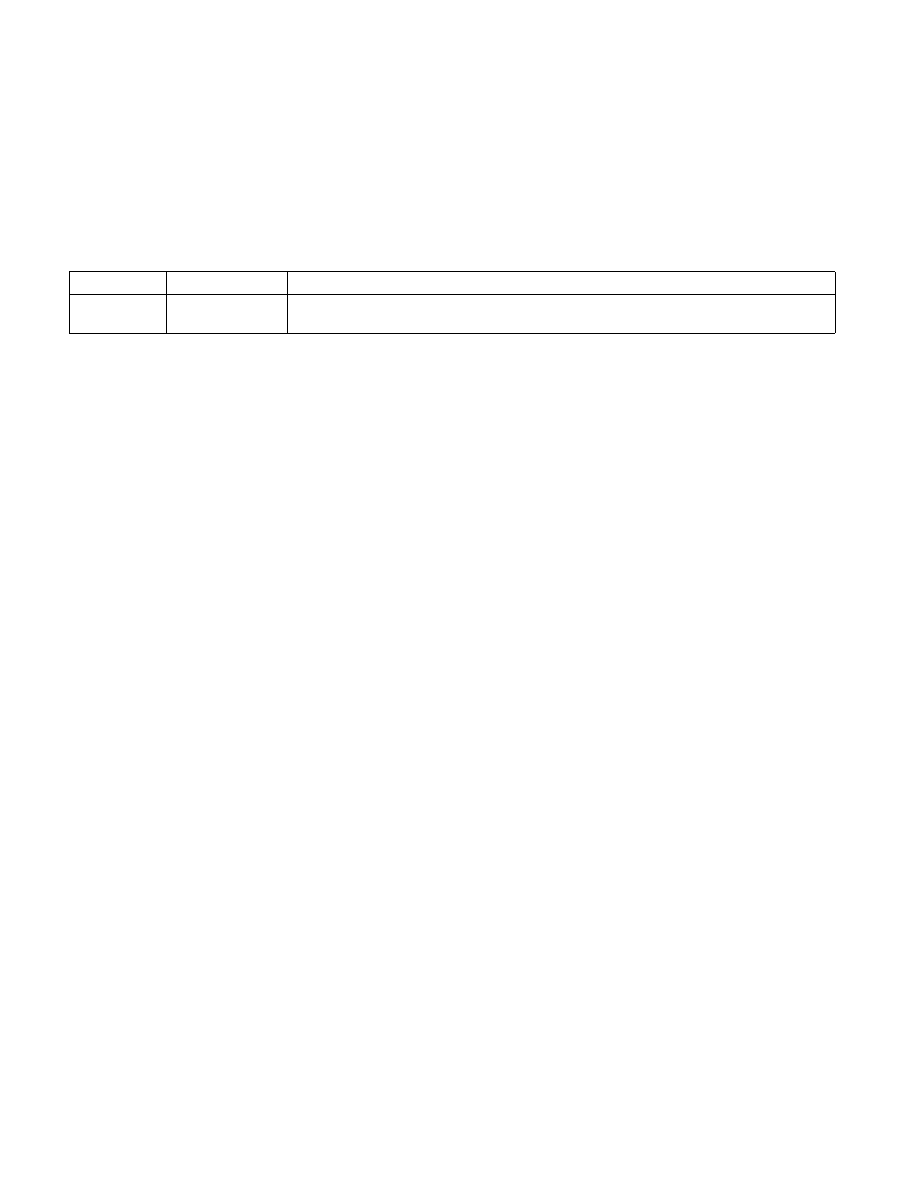

Table 24-9. Definitions of VM-Function Controls

Bit Position(s) Name

Description

0

EPTP switching

The EPTP-switching VM function changes the EPT pointer to a value chosen from the EPTP list.