Vol. 3C 24-15

VIRTUAL MACHINE CONTROL STRUCTURES

24.6.11 Extended-Page-Table Pointer (EPTP)

The extended-page-table pointer (EPTP) contains the address of the base of EPT PML4 table (see Section

28.2.2), as well as other EPT configuration information. The format of this field is shown in Table 24-8.

The EPTP exists only on processors that support the 1-setting of the “enable EPT” VM-execution control.

24.6.12 Virtual-Processor Identifier (VPID)

The virtual-processor identifier (VPID) is a 16-bit field. It exists only on processors that support the 1-setting

of the “enable VPID” VM-execution control. See Section 28.1 for details regarding the use of this field.

24.6.13 Controls for PAUSE-Loop Exiting

On processors that support the 1-setting of the “PAUSE-loop exiting” VM-execution control, the VM-execution

control fields include the following 32-bit fields:

•

PLE_Gap. Software can configure this field as an upper bound on the amount of time between two successive

executions of PAUSE in a loop.

•

PLE_Window. Software can configure this field as an upper bound on the amount of time a guest is allowed to

execute in a PAUSE loop.

These fields measure time based on a counter that runs at the same rate as the timestamp counter (TSC). See

Section 25.1.3 for more details regarding PAUSE-loop exiting.

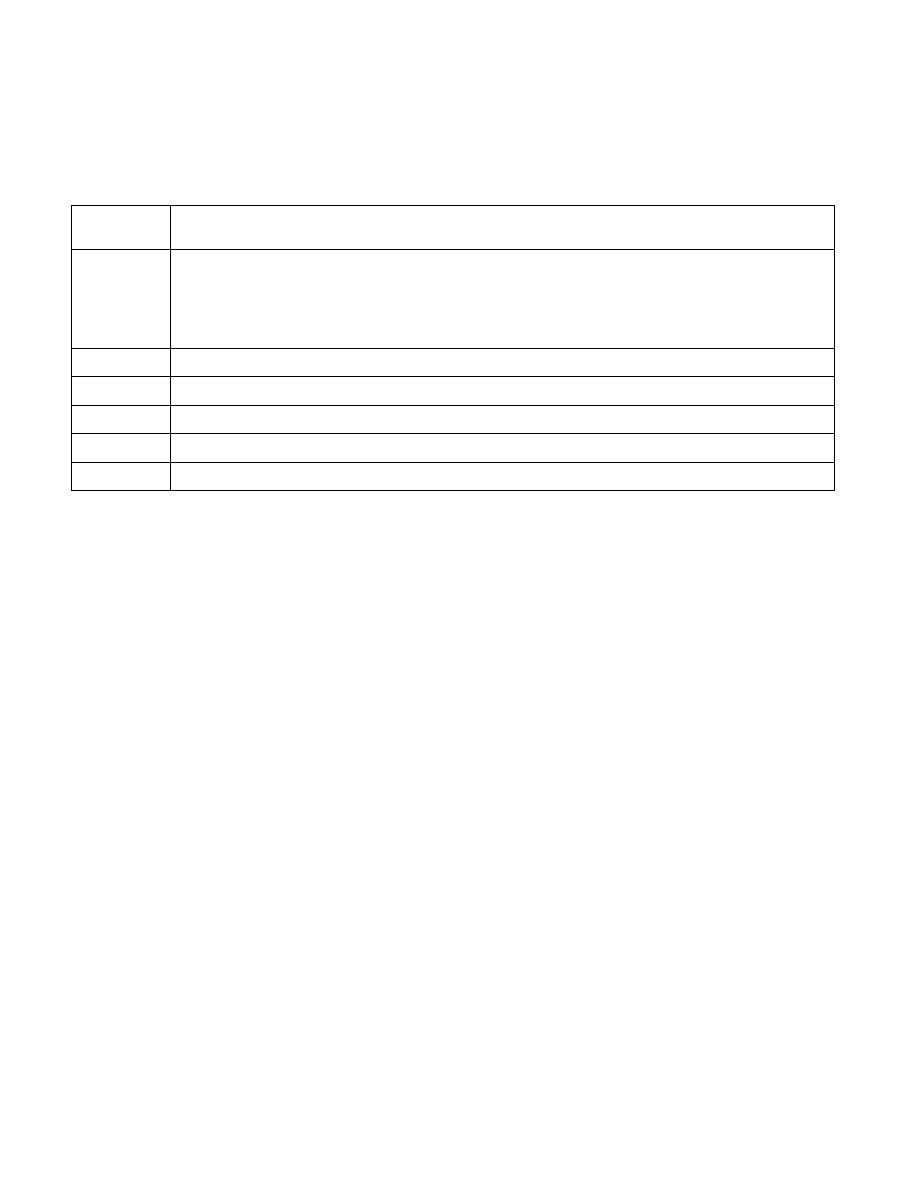

Table 24-8. Format of Extended-Page-Table Pointer

Bit

Position(s)

Field

2:0

EPT paging-structure memory type (see Section 28.2.6):

0 = Uncacheable (UC)

6 = Write-back (WB)

Other values are reserved.

1

NOTES:

1. Software should read the VMX capability MSR IA32_VMX_EPT_VPID_CAP (see Appendix A.10) to determine what EPT paging-struc-

ture memory types are supported.

5:3

This value is 1 less than the EPT page-walk length (see Section 28.2.2)

6

Setting this control to 1 enables accessed and dirty flags for EPT (see Section 28.2.4)

2

2. Not all processors support accessed and dirty flags for EPT. Software should read the VMX capability MSR

IA32_VMX_EPT_VPID_CAP (see Appendix A.10) to determine whether the processor supports this feature.

11:7

Reserved

N–1:12

Bits N–1:12 of the physical address of the 4-KByte aligned EPT PML4 table

3

3. N is the physical-address width supported by the logical processor. Software can determine a processor’s physical-address width by

executing CPUID with 80000008H in EAX. The physical-address width is returned in bits 7:0 of EAX.

63:N

Reserved