6-8 Vol. 3A

INTERRUPT AND EXCEPTION HANDLING

6.9

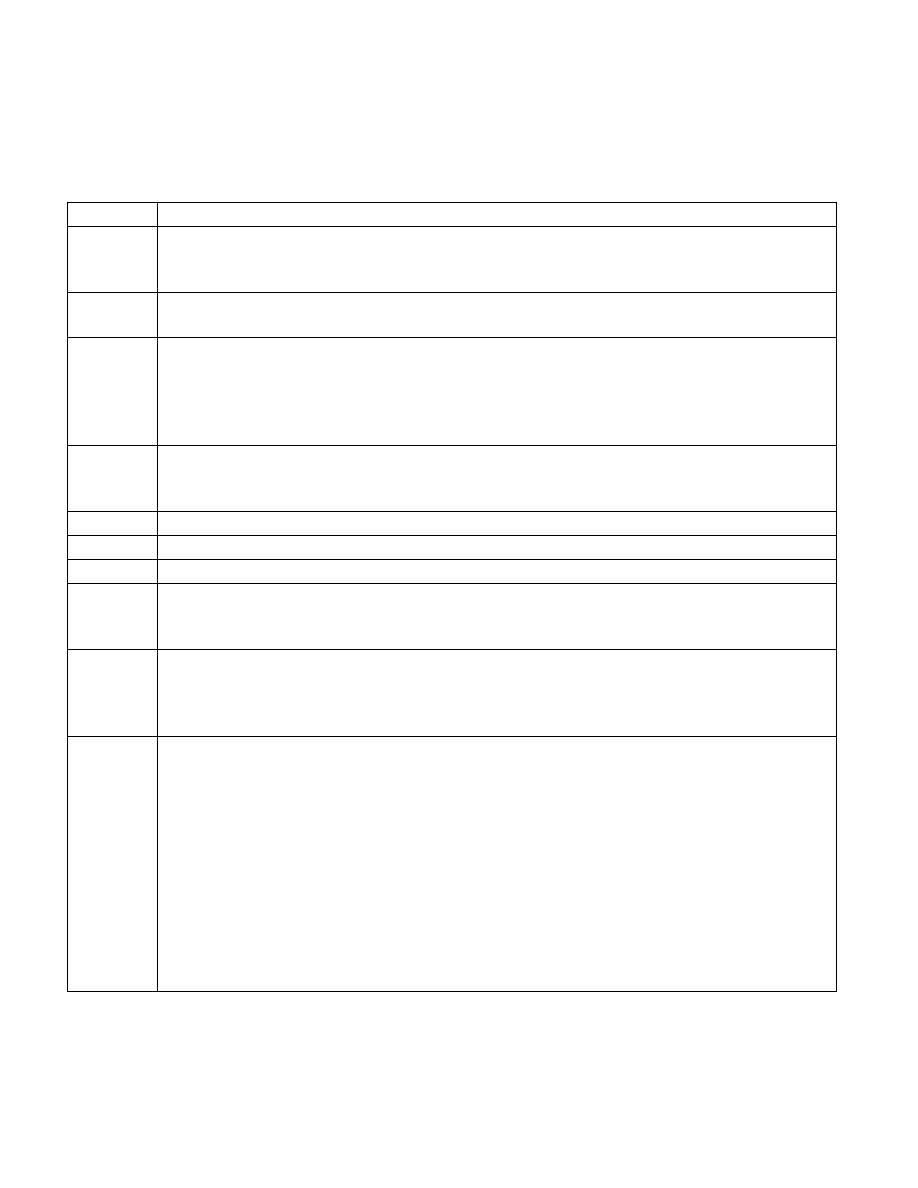

PRIORITY AMONG SIMULTANEOUS EXCEPTIONS AND INTERRUPTS

If more than one exception or interrupt is pending at an instruction boundary, the processor services them in a

predictable order. Table 6-2 shows the priority among classes of exception and interrupt sources.

While priority among these classes listed in Table 6-2 is consistent throughout the architecture, exceptions within

each class are implementation-dependent and may vary from processor to processor. The processor first services

Table 6-2. Priority Among Simultaneous Exceptions and Interrupts

Priority

Description

1 (Highest)

Hardware Reset and Machine Checks

- RESET

- Machine Check

2

Trap on Task Switch

- T flag in TSS is set

3

External Hardware Interventions

- FLUSH

- STOPCLK

- SMI

- INIT

4

Traps on the Previous Instruction

- Breakpoints

- Debug Trap Exceptions (TF flag set or data/I-O breakpoint)

5

Nonmaskable Interrupts (NMI)

1

6

Maskable Hardware Interrupts

1

7

Code Breakpoint Fault

8

Faults from Fetching Next Instruction

- Code-Segment Limit Violation

- Code Page Fault

9

Faults from Decoding the Next Instruction

- Instruction length > 15 bytes

- Invalid Opcode

- Coprocessor Not Available

10 (Lowest)

Faults on Executing an Instruction

- Overflow

- Bound error

- Invalid TSS

- Segment Not Present

- Stack fault

- General Protection

- Data Page Fault

- Alignment Check

- x87 FPU Floating-point exception

- SIMD floating-point exception

- Virtualization exception

NOTE

1. The Intel® 486 processor and earlier processors group nonmaskable and maskable interrupts in the same priority class.