3-16 Vol. 3A

PROTECTED-MODE MEMORY MANAGEMENT

processor to store an aligned word, followed by an aligned doubleword. User-mode programs normally do not store

pseudo-descriptors, but the possibility of generating an alignment check fault can be avoided by aligning pseudo-

descriptors in this way. The same alignment should be used when storing the IDTR register using the SIDT instruc-

tion. When storing the LDTR or task register (using the SLDT or STR instruction, respectively), the pseudo-

descriptor should be located at a doubleword address (that is, address MOD 4 is equal to 0).

3.5.2

Segment Descriptor Tables in IA-32e Mode

In IA-32e mode, a segment descriptor table can contain up to 8192 (2

13

) 8-byte descriptors. An entry in the

segment descriptor table can be 8 bytes. System descriptors are expanded to 16 bytes (occupying the space of two

entries).

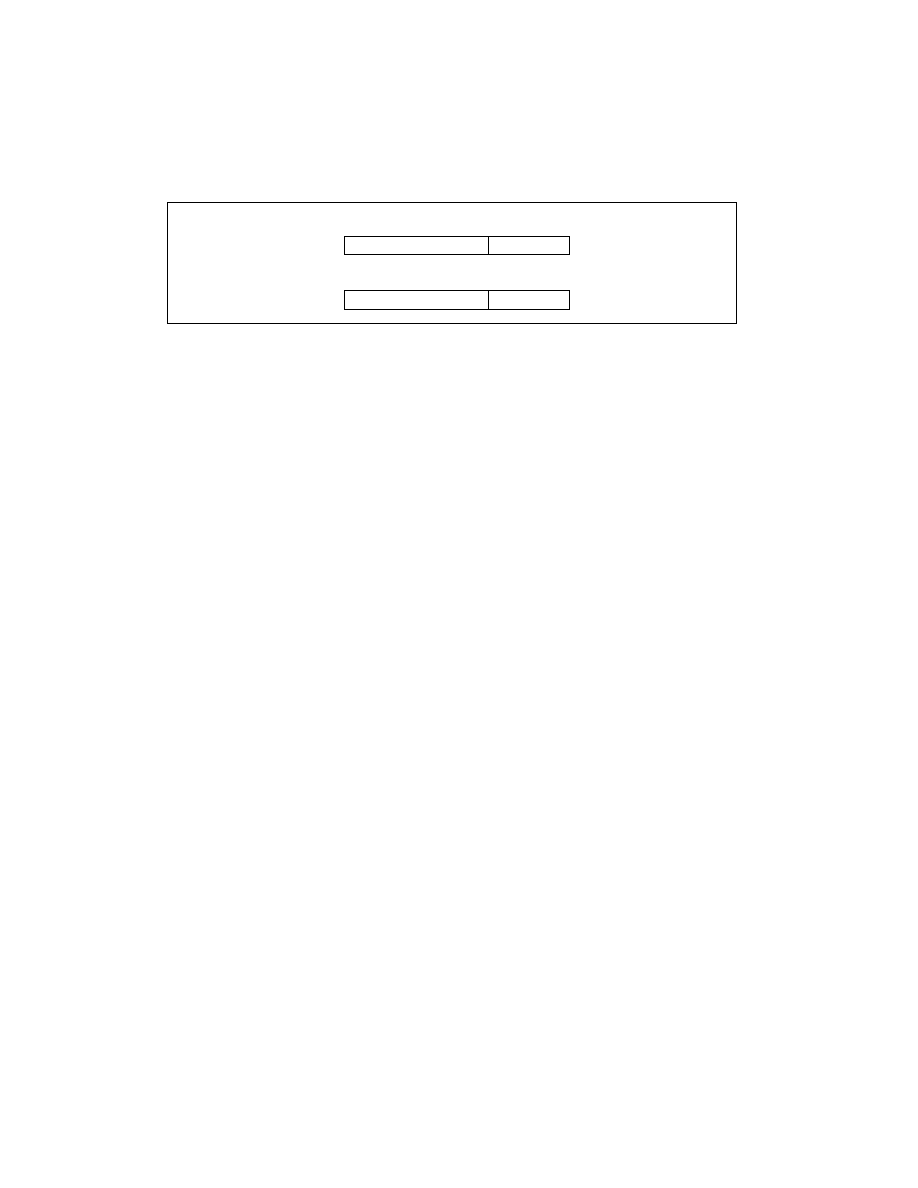

GDTR and LDTR registers are expanded to hold 64-bit base address. The corresponding pseudo-descriptor is 80

bits. (see the bottom diagram in Figure 3-11).

The following system descriptors expand to 16 bytes:

— Call gate descriptors (see Section 5.8.3.1, “IA-32e Mode Call Gates”)

— IDT gate descriptors (see Section 6.14.1, “64-Bit Mode IDT”)

— LDT and TSS descriptors (see Section 7.2.3, “TSS Descriptor in 64-bit mode”).

Figure 3-11. Pseudo-Descriptor Formats

0

32-bit Base Address

Limit

47

15

16

0

64-bit Base Address

Limit

79

15

16