Vol. 2A 2-21

INSTRUCTION FORMAT

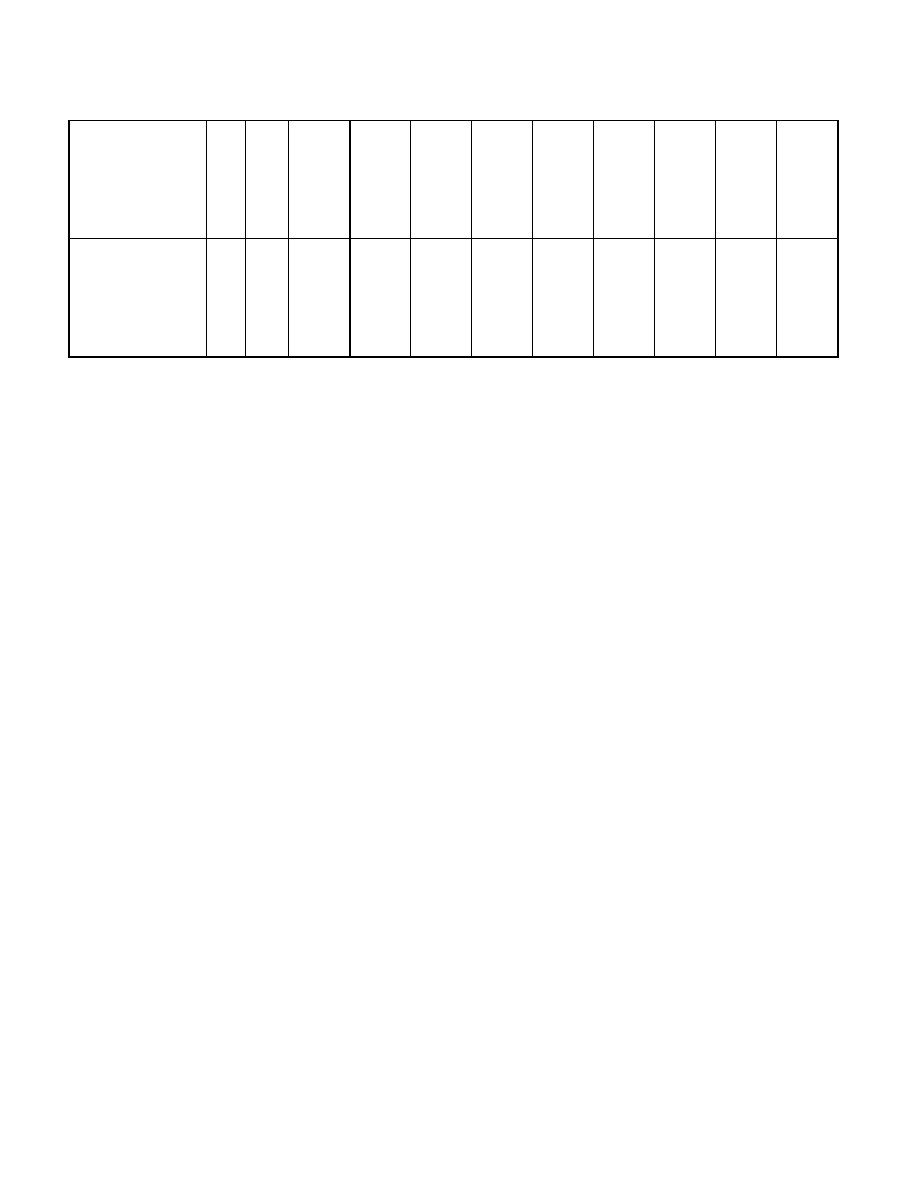

2.3.12.1 64-bit Mode VSIB Memory Addressing

In 64-bit mode VSIB memory addressing uses the VEX.B field and the base field of the SIB byte to encode one of

the 16 general-purpose register as the base register. The VEX.X field and the index field of the SIB byte encode one

of the 16 vector registers as the vector index register.

In 64-bit mode the top row of Table 2-13 base register should be interpreted as the full 64-bit of each register.

2.4

AVX AND SSE INSTRUCTION EXCEPTION SPECIFICATION

To look up the exceptions of legacy 128-bit SIMD instruction, 128-bit VEX-encoded instructions, and 256-bit VEX-

encoded instruction, Table 2-14 summarizes the exception behavior into separate classes, with detailed exception

conditions defined in sub-sections 2.4.1 through 2.5.1. For example, ADDPS contains the entry:

“See Exceptions Type 2”

In this entry, “Type2” can be looked up in Table 2-14.

The instruction’s corresponding CPUID feature flag can be identified in the fourth column of the Instruction

summary table.

Note: #UD on CPUID feature flags=0 is not guaranteed in a virtualized environment if the hardware supports the

feature flag.

NOTE

Instructions that operate only with MMX, X87, or general-purpose registers are not covered by the

exception classes defined in this section. For instructions that operate on MMX registers, see

Section 22.25.3, “Exception Conditions of Legacy SIMD Instructions Operating on MMX Registers”

in the Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 3B.

VR0/VR8

VR1/VR9

VR2/VR10

VR3/VR11

VR4/VR12

VR5/VR13

VR6/VR14

VR7/VR15

*4

10

000

001

010

011

100

101

110

111

80

88

90

98

A0

A8

B0

B8

81

89

91

89

A1

A9

B1

B9

82

8A

92

9A

A2

AA

B2

BA

83

8B

93

9B

A3

AB

B3

BB

84

8C

94

9C

A4

AC

B4

BC

85

8D

95

9D

A5

AD

B5

BD

86

8E

96

9E

A6

AE

B6

BE

87

8F

97

9F

A7

AF

B7

BF

VR0/VR8

VR1/VR9

VR2/VR10

VR3/VR11

VR4/VR12

VR5/VR13

VR6/VR14

VR7/VR15

*8

11

000

001

010

011

100

101

110

111

C0

C8

D0

D8

E0

E8

F0

F8

C1

C9

D1

D9

E1

E9

F1

F9

C2

CA

D2

DA

E2

EA

F2

FA

C3

CB

D3

DB

E3

EB

F3

FB

C4

CC

D4

DC

E4

EC

F4

FC

C5

CD

D5

DD

E5

ED

F5

FD

C6

CE

D6

DE

E6

EE

F6

FE

C7

CF

D7

DF

E7

EF

F7

FF

NOTES:

1. If ModR/M.mod = 00b, the base address is zero, then effective address is computed as [scaled vector index] + disp32. Otherwise the

base address is computed as [EBP/R13]+ disp, the displacement is either 8 bit or 32 bit depending on the value of ModR/M.mod:

MOD Effective

Address

00b

[Scaled Vector Register] + Disp32

01b

[Scaled Vector Register] + Disp8 + [EBP/R13]

10b

[Scaled Vector Register] + Disp32 + [EBP/R13]

Table 2-13. 32-Bit VSIB Addressing Forms of the SIB Byte (Contd.)