2-26 Vol. 2A

INSTRUCTION FORMAT

2.4.1

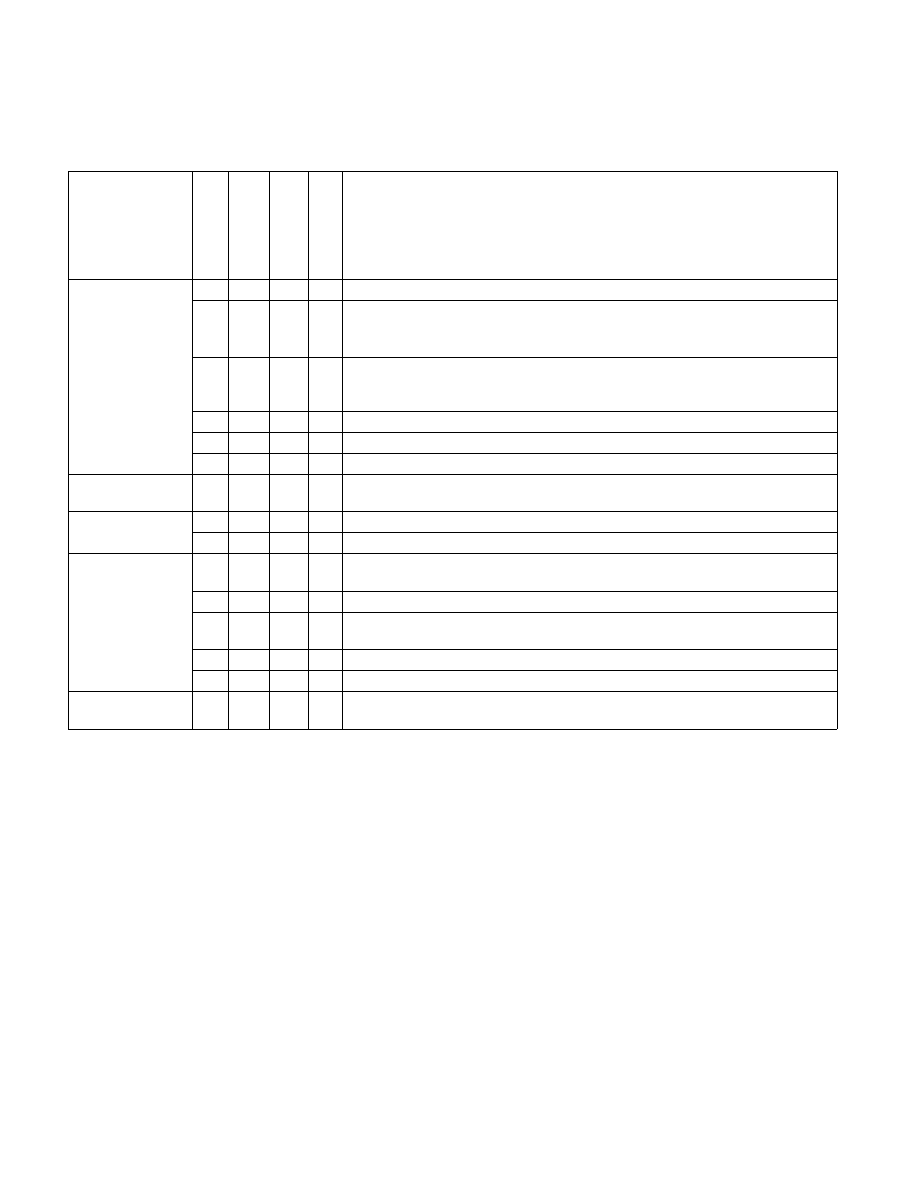

Exceptions Type 1 (Aligned memory reference)

Table 2-18. Type 1 Class Exception Conditions

Exception

Re

al

V

irtual-808

6

Pr

ot

ec

ted

and

Co

mp

ati

bil

ity

64-b

it

Cause of Exception

Invalid Opcode,

#UD

X

X

VEX prefix.

X

X

VEX prefix:

If XCR0[2:1]

≠

‘11b’.

If CR4.OSXSAVE[bit 18]=0.

X

X

X

X

Legacy SSE instruction:

If CR0.EM[bit 2] = 1.

If CR4.OSFXSR[bit 9] = 0.

X

X

X

X

If preceded by a LOCK prefix (F0H).

X

X

If any REX, F2, F3, or 66 prefixes precede a VEX prefix.

X

X

X

X

If any corresponding CPUID feature flag is ‘0’.

Device Not Avail-

able, #NM

X

X

X

X

If CR0.TS[bit 3]=1.

Stack, SS(0)

X

For an illegal address in the SS segment.

X

If a memory address referencing the SS segment is in a non-canonical form.

General Protec-

tion, #GP(0)

X

X

VEX.256: Memory operand is not 32-byte aligned.

VEX.128: Memory operand is not 16-byte aligned.

X

X

X

X

Legacy SSE: Memory operand is not 16-byte aligned.

X

For an illegal memory operand effective address in the CS, DS, ES, FS or GS seg-

ments.

X

If the memory address is in a non-canonical form.

X

X

If any part of the operand lies outside the effective address space from 0 to FFFFH.

Page Fault

#PF(fault-code)

X

X

X

For a page fault.