15-6 Vol. 1

PROGRAMMING WITH INTEL® AVX-512

Software must follow the detection procedure for the 512-bit AVX-512 Foundation instructions as described in

Section 15.2.

Detection of other 512-bit sibling instruction groups listed in Table 15-1 (excluding AVX512F) follows the procedure

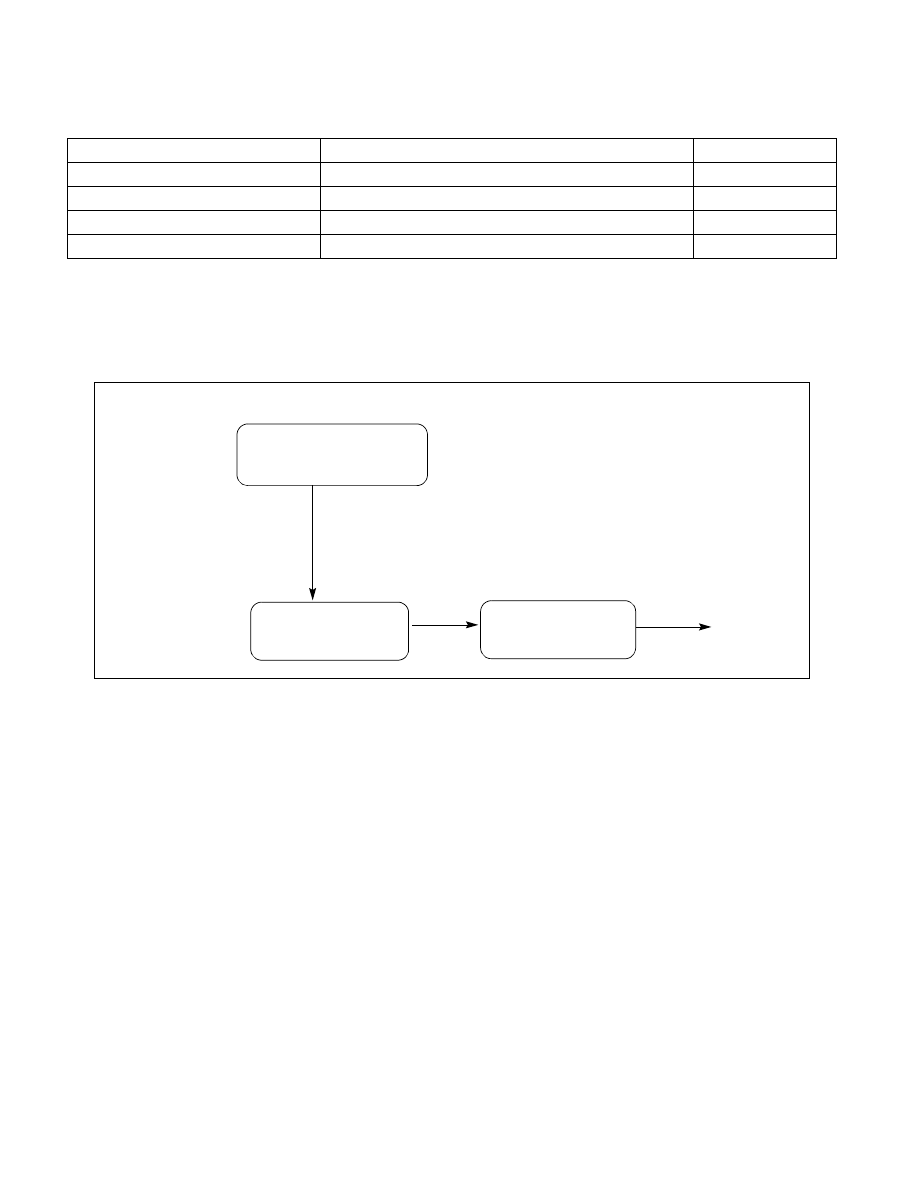

described in Figure 15-4:

To detect 512-bit instructions enumerated by AVX512CD, the following sequence is strongly recommended.

1. Detect CPUID.1:ECX.OSXSAVE[bit 27] = 1 (XGETBV enabled for application use).

2. Execute XGETBV and verify that XCR0[7:5] = ‘111b’ (OPMASK state, upper 256-bit of ZMM0-ZMM15 and

ZMM16-ZMM31 state are enabled by OS) and that XCR0[2:1] = ‘11b’ (XMM state and YMM state are enabled by

OS).

3. Verify both CPUID.0x7.0:EBX.AVX512F[bit 16] = 1, CPUID.0x7.0:EBX.AVX512CD[bit 28] = 1.

Similarly, the detection procedure for enumerating 512-bit instructions reported by AVX512DW follows the same

flow.

15.4

DETECTION OF INTEL AVX-512 INSTRUCTION GROUPS OPERATING AT 256

AND 128-BIT VECTOR LENGTHS

For each of the 512-bit instruction groups in the Intel AVX-512 family listed in Table 15-1, the EVEX encoding

scheme may support a vast majority of these instructions operating at 256-bit or 128-bit (if applicable) vector

lengths. Encoding support for vector lengths smaller than 512-bits is indicated by CPUID.(EAX=07H,

ECX=0):EBX[bit 31], abbreviated as AVX512VL.

Table 15-1. 512-bit Instruction Groups in the Intel AVX-512 Family

CPUID Leaf 7 Feature Flag Bit

Feature Flag abbreviation of 512-bit Instruction Group

SW Detection Flow

CPUID.(EAX=07H, ECX=0):EBX[bit 16]

AVX512F (AVX-512 Foundation)

CPUID.(EAX=07H, ECX=0):EBX[bit 28]

AVX512CD

CPUID.(EAX=07H, ECX=0):EBX[bit 17]

AVX512DQ

CPUID.(EAX=07H, ECX=0):EBX[bit 30]

AVX512BW

Figure 15-4. Procedural Flow for Application Detection of 512-bit Instruction Groups

Implied HW support for

Check enabled state in

XCR0 via XGETBV

Check AVX512F and

a sibling 512-bit flag

Check feature flag

CPUID.1H:ECX.OXSAVE = 1?

OS provides processor

extended state management

States

ok to use

XSAVE, XRSTOR, XGETBV, XCR0

enabled

Instructions

Yes

YMM,ZMM

Opmask,