4-18 Vol. 1

DATA TYPES

The round up and round down modes are termed directed rounding and can be used to implement interval arith-

metic. Interval arithmetic is used to determine upper and lower bounds for the true result of a multistep computa-

tion, when the intermediate results of the computation are subject to rounding.

The round toward zero mode (sometimes called the “chop” mode) is commonly used when performing integer

arithmetic with the x87 FPU.

The rounded result is called the inexact result. When the processor produces an inexact result, the floating-point

precision (inexact) flag (PE) is set (see Section 4.9.1.6, “Inexact-Result (Precision) Exception (#P)”).

The rounding modes have no effect on comparison operations, operations that produce exact results, or operations

that produce NaN results.

4.8.4.1

Rounding Control (RC) Fields

In the Intel 64 and IA-32 architectures, the rounding mode is controlled by a 2-bit rounding-control (RC) field

(Table 4-8 shows the encoding of this field). The RC field is implemented in two different locations:

•

x87 FPU control register (bits 10 and 11)

•

The MXCSR register (bits 13 and 14)

Although these two RC fields perform the same function, they control rounding for different execution environ-

ments within the processor. The RC field in the x87 FPU control register controls rounding for computations

performed with the x87 FPU instructions; the RC field in the MXCSR register controls rounding for SIMD floating-

point computations performed with the SSE/SSE2 instructions.

4.8.4.2

Truncation with SSE and SSE2 Conversion Instructions

The following SSE/SSE2 instructions automatically truncate the results of conversions from floating-point values to

integers when the result it inexact: CVTTPD2DQ, CVTTPS2DQ, CVTTPD2PI, CVTTPS2PI, CVTTSD2SI, CVTTSS2SI.

Here, truncation means the round toward zero mode described in Table 4-8.

4.9

OVERVIEW OF FLOATING-POINT EXCEPTIONS

The following section provides an overview of floating-point exceptions and their handling in the IA-32 architecture.

For information specific to the x87 FPU and to the SSE/SSE2/SSE3/SSE4.1 extensions, refer to the following

sections:

•

Section 8.4, “x87 FPU Floating-Point Exception Handling”

•

Section 11.5, “SSE, SSE2, and SSE3 Exceptions”

When operating on floating-point operands, the IA-32 architecture recognizes and detects six classes of exception

conditions:

•

Invalid operation (#I)

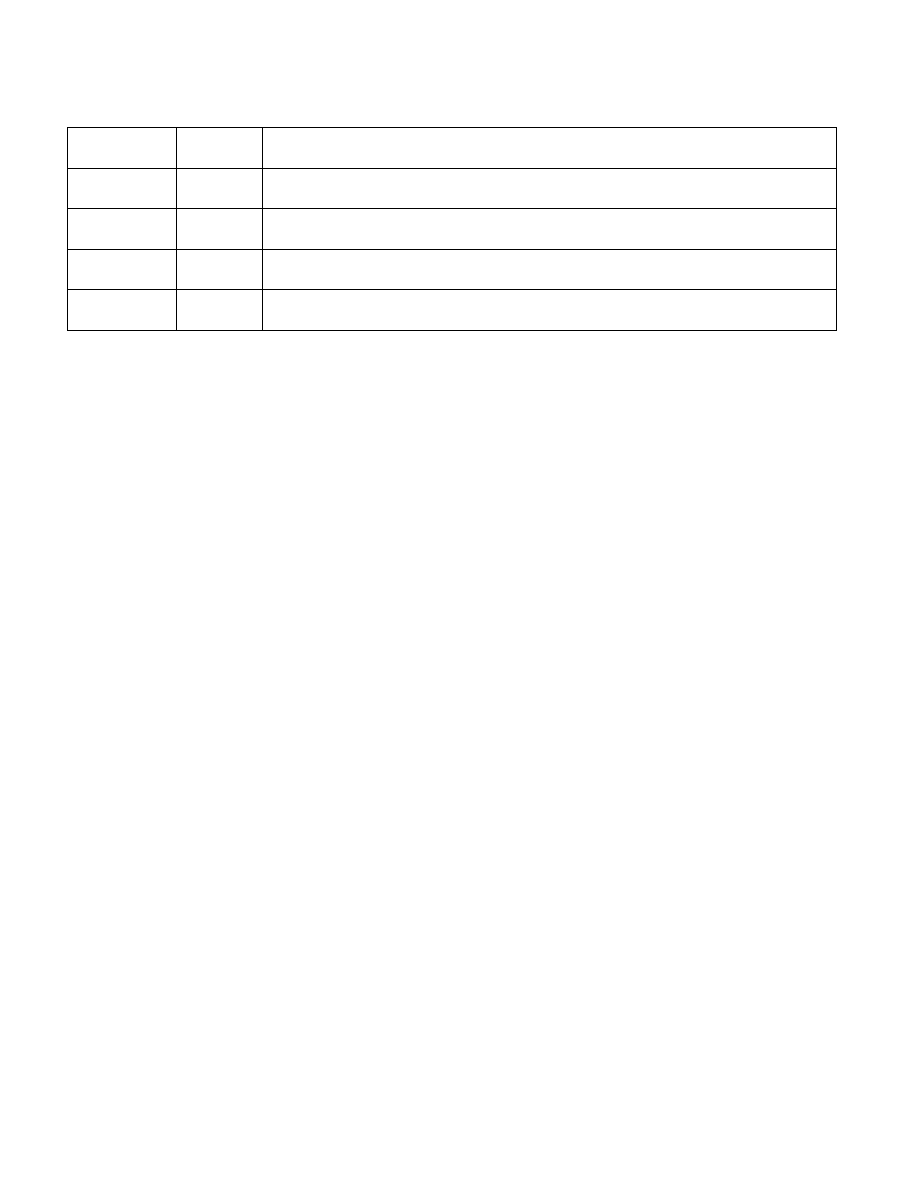

Table 4-8. Rounding Modes and Encoding of Rounding Control (RC) Field

Rounding Mode

RC Field

Setting

Description

Round to

nearest (even)

00B

Rounded result is the closest to the infinitely precise result. If two values are equally close, the

result is the even value (that is, the one with the least-significant bit of zero). Default

Round down

(toward −∞)

01B

Rounded result is closest to but no greater than the infinitely precise result.

Round up

(toward +∞)

10B

Rounded result is closest to but no less than the infinitely precise result.

Round toward

zero (Truncate)

11B

Rounded result is closest to but no greater in absolute value than the infinitely precise result.