19-204 Vol. 3B

PERFORMANCE-MONITORING EVENTS

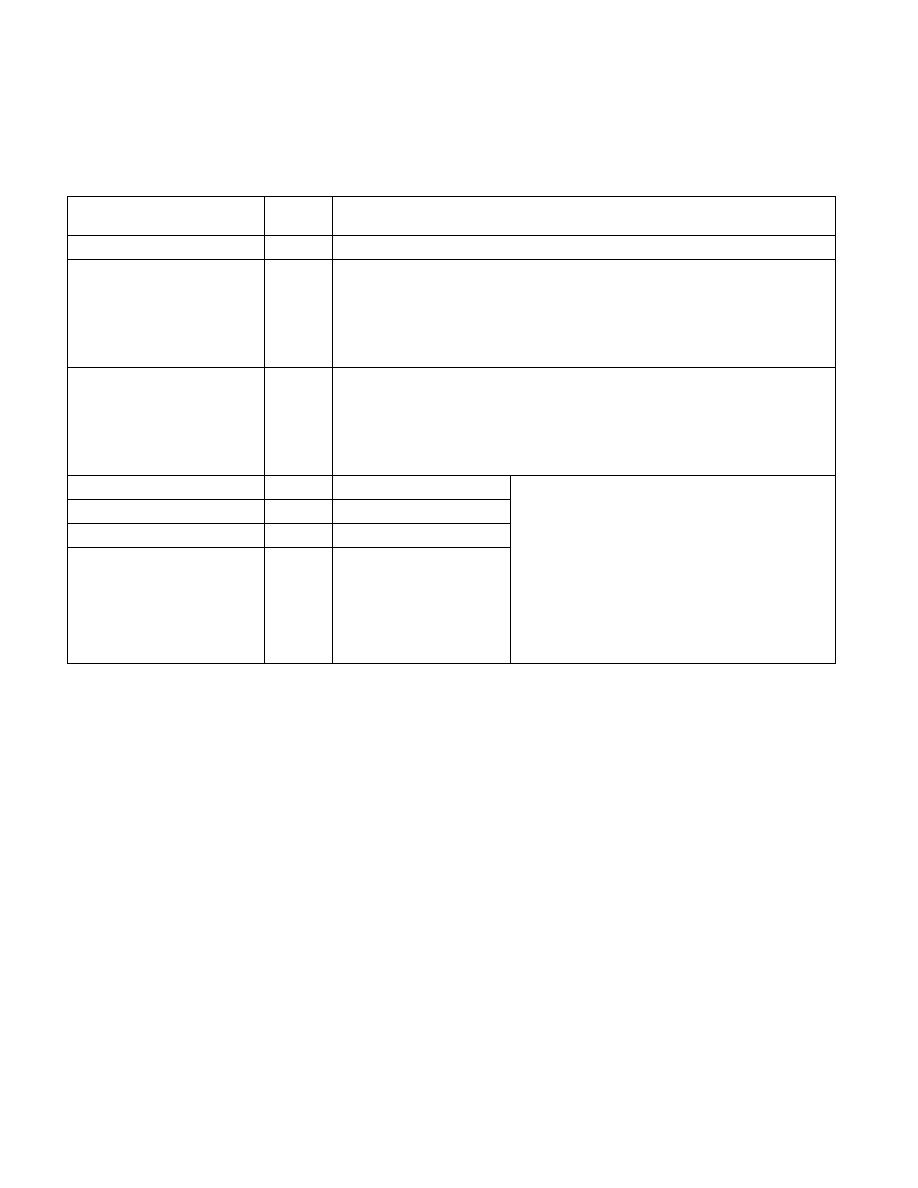

A number of P6 family processor performance monitoring events are modified for the Pentium M processor. Table

19-36 lists the performance monitoring events that were changed in the Pentium M processor, and differ from

performance monitoring events for the P6 family of processors.

19.17 P6 FAMILY PROCESSOR PERFORMANCE-MONITORING EVENTS

Table 19-37 lists the events that can be counted with the performance-monitoring counters and read with the

RDPMC instruction for the P6 family processors. The unit column gives the microarchitecture or bus unit that

produces the event; the event number column gives the hexadecimal number identifying the event; the mnemonic

event name column gives the name of the event; the unit mask column gives the unit mask required (if any); the

description column describes the event; and the comments column gives additional information about the event.

All of these performance events are model specific for the P6 family processors and are not available in this form in

the Pentium 4 processors or the Pentium processors. Some events (such as those added in later generations of the

P6 family processors) are only available in specific processors in the P6 family. All performance event encodings not

listed in Table 19-37 are reserved and their use will result in undefined counter results.

See the end of the table for notes related to certain entries in the table.

Table 19-36. Performance Monitoring Events Modified on Intel

®

Pentium

®

M Processors

Name Hex

Values

Descriptions

CPU_CLK_UNHALTED

79H

Number of cycles during which the processor is not halted, and not in a thermal trip.

EMON_SSE_SSE2_INST_

RETIRED

D8H

Streaming SIMD Extensions Instructions Retired:

Mask = 0 – SSE packed single and scalar single

Mask = 1 – SSE scalar-single

Mask = 2 – SSE2 packed-double

Mask = 3 – SSE2 scalar-double

EMON_SSE_SSE2_COMP_INST_

RETIRED

D9H

Computational SSE Instructions Retired:

Mask = 0 – SSE packed single

Mask = 1 – SSE Scalar-single

Mask = 2 – SSE2 packed-double

Mask = 3 – SSE2 scalar-double

L2_LD

29H

L2 data loads

Mask[0] = 1 – count I state lines

Mask[1] = 1 – count S state lines

Mask[2] = 1 – count E state lines

Mask[3] = 1 – count M state lines

Mask[5:4]:

00H – Excluding hardware-prefetched lines

01H - Hardware-prefetched lines only

02H/03H – All (HW-prefetched lines and non HW --

Prefetched lines)

L2_LINES_IN

24H

L2 lines allocated

L2_LINES_OUT

26H

L2 lines evicted

L2_M_LINES_OUT

27H

Lw M-state lines evicted