Vol. 3B 19-205

PERFORMANCE-MONITORING EVENTS

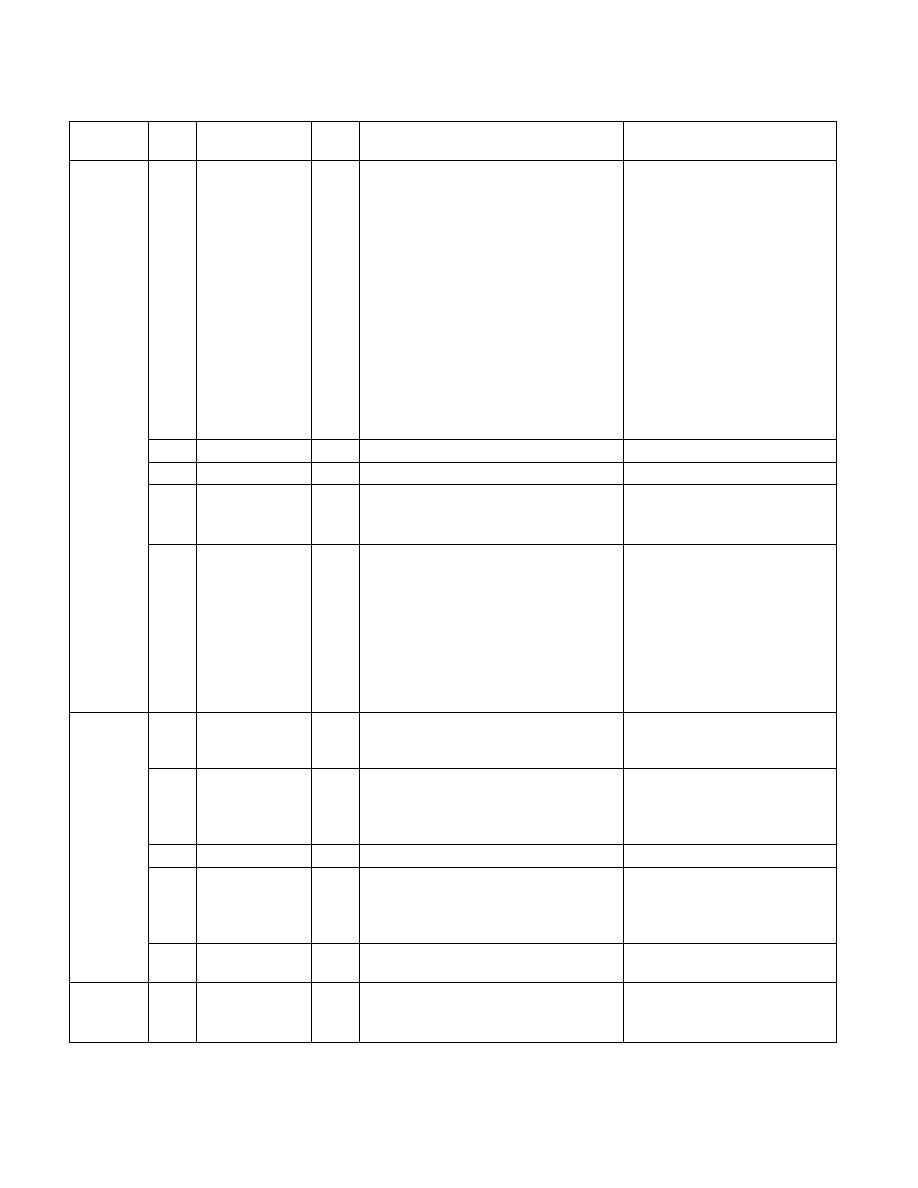

Table 19-37. Events That Can Be Counted with the P6 Family Performance-Monitoring Counters

Unit

Event

Num.

Mnemonic Event

Name

Unit

Mask Description

Comments

Data Cache

Unit (DCU)

43H

DATA_MEM_REFS 00H

All loads from any memory type. All stores

to any memory type. Each part of a split is

counted separately. The internal logic counts

not only memory loads and stores, but also

internal retries.

80-bit floating-point accesses are double

counted, since they are decomposed into a

16-bit exponent load and a 64-bit mantissa

load. Memory accesses are only counted

when they are actually performed (such as a

load that gets squashed because a previous

cache miss is outstanding to the same

address, and which finally gets performed, is

only counted once).

Does not include I/O accesses, or other

nonmemory accesses.

45H

DCU_LINES_IN

00H

Total lines allocated in DCU.

46H

DCU_M_LINES_IN 00H

Number of M state lines allocated in DCU.

47H

DCU_M_LINES_

OUT

00H

Number of M state lines evicted from DCU.

This includes evictions via snoop HITM,

intervention or replacement.

48H

DCU_MISS_

OUTSTANDING

00H

Weighted number of cycles while a DCU miss

is outstanding, incremented by the number

of outstanding cache misses at any

particular time.

Cacheable read requests only are

considered.

Uncacheable requests are excluded.

Read-for-ownerships are counted, as well as

line fills, invalidates, and stores.

An access that also misses the L2

is short-changed by 2 cycles (i.e., if

counts N cycles, should be N+2

cycles).

Subsequent loads to the same

cache line will not result in any

additional counts.

Count value not precise, but still

useful.

Instruction

Fetch Unit

(IFU)

80H

IFU_IFETCH

00H

Number of instruction fetches, both

cacheable and noncacheable, including UC

fetches.

81H

IFU_IFETCH_

MISS

00H

Number of instruction fetch misses

All instruction fetches that do not hit the IFU

(i.e., that produce memory requests). This

includes UC accesses.

85H

ITLB_MISS

00H

Number of ITLB misses.

86H

IFU_MEM_STALL

00H

Number of cycles instruction fetch is stalled,

for any reason.

Includes IFU cache misses, ITLB misses, ITLB

faults, and other minor stalls.

87H

ILD_STALL

00H

Number of cycles that the instruction length

decoder is stalled.

L2 Cache

1

28H

L2_IFETCH

MESI

0FH

Number of L2 instruction fetches.

This event indicates that a normal

instruction fetch was received by the L2.