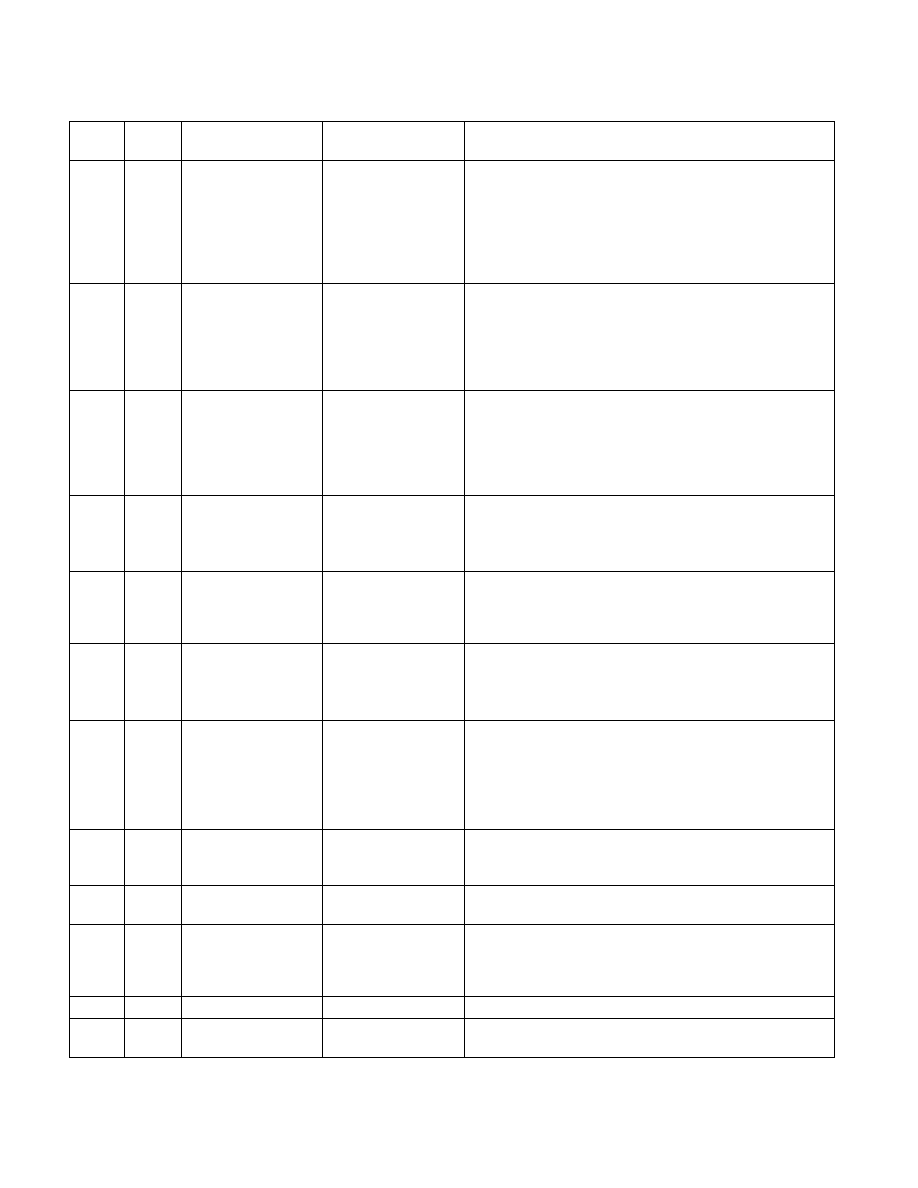

19-162 Vol. 3B

PERFORMANCE-MONITORING EVENTS

6FH

See

and

BUS_TRANS_MEM

Memory bus

transactions.

This event counts all memory bus transactions including:

- Burst transactions.

- Partial reads and writes.

- Invalidate transactions.

The BUS_TRANS_MEM count is the sum of

BUS_TRANS_BURST, BUS_TRANS_P and BUS_TRANS_INVAL.

70H

See

and

BUS_TRANS_ANY

All bus transactions.

This event counts all bus transactions. This includes:

- Memory transactions.

- IO transactions (non memory-mapped).

- Deferred transaction completion.

- Other less frequent transactions, such as interrupts.

77H

See

and

EXT_SNOOP

External snoops.

This event counts the snoop responses to bus transactions.

Responses can be counted separately by type and by bus agent.

Note: This event is thread-independent and will not provide a

count per logical processor when AnyThr is disabled.

7AH

See

BUS_HIT_DRV

HIT signal asserted.

This event counts the number of bus cycles during which the

processor drives the HIT# pin to signal HIT snoop response.

Note: This event is thread-independent and will not provide a

count per logical processor when AnyThr is disabled.

7BH

See

BUS_HITM_DRV

HITM signal asserted.

This event counts the number of bus cycles during which the

processor drives the HITM# pin to signal HITM snoop response.

NOTE: This event is thread-independent and will not provide a

count per logical processor when AnyThr is disabled.

7DH

See

BUSQ_EMPTY

Bus queue is empty.

This event counts the number of cycles during which the core

did not have any pending transactions in the bus queue.

Note: This event is thread-independent and will not provide a

count per logical processor when AnyThr is disabled.

7EH

See

and

SNOOP_STALL_DRV

Bus stalled for snoops. This event counts the number of times that the bus snoop stall

signal is asserted. During the snoop stall cycles no new bus

transactions requiring a snoop response can be initiated on the

bus.

Note: This event is thread-independent and will not provide a

count per logical processor when AnyThr is disabled.

7FH

See

BUS_IO_WAIT

IO requests waiting in

the bus queue.

This event counts the number of core cycles during which IO

requests wait in the bus queue. This event counts IO requests

from the core.

80H

03H

ICACHE.ACCESSES

Instruction fetches.

This event counts all instruction fetches, including uncacheable

fetches.

80H

02H

ICACHE.MISSES

Icache miss.

This event counts all instruction fetches that miss the

Instruction cache or produce memory requests. This includes

uncacheable fetches. An instruction fetch miss is counted only

once and not once for every cycle it is outstanding.

82H

04H

ITLB.FLUSH

ITLB flushes.

This event counts the number of ITLB flushes.

82H

02H

ITLB.MISSES

ITLB misses.

This event counts the number of instruction fetches that miss

the ITLB.

Table 19-26. Non-Architectural Performance Events for 45 nm, 32 nm Intel® Atom™ Processors (Contd.)

Event

Num.

Umask

Value

Event Name

Definition

Description and Comment