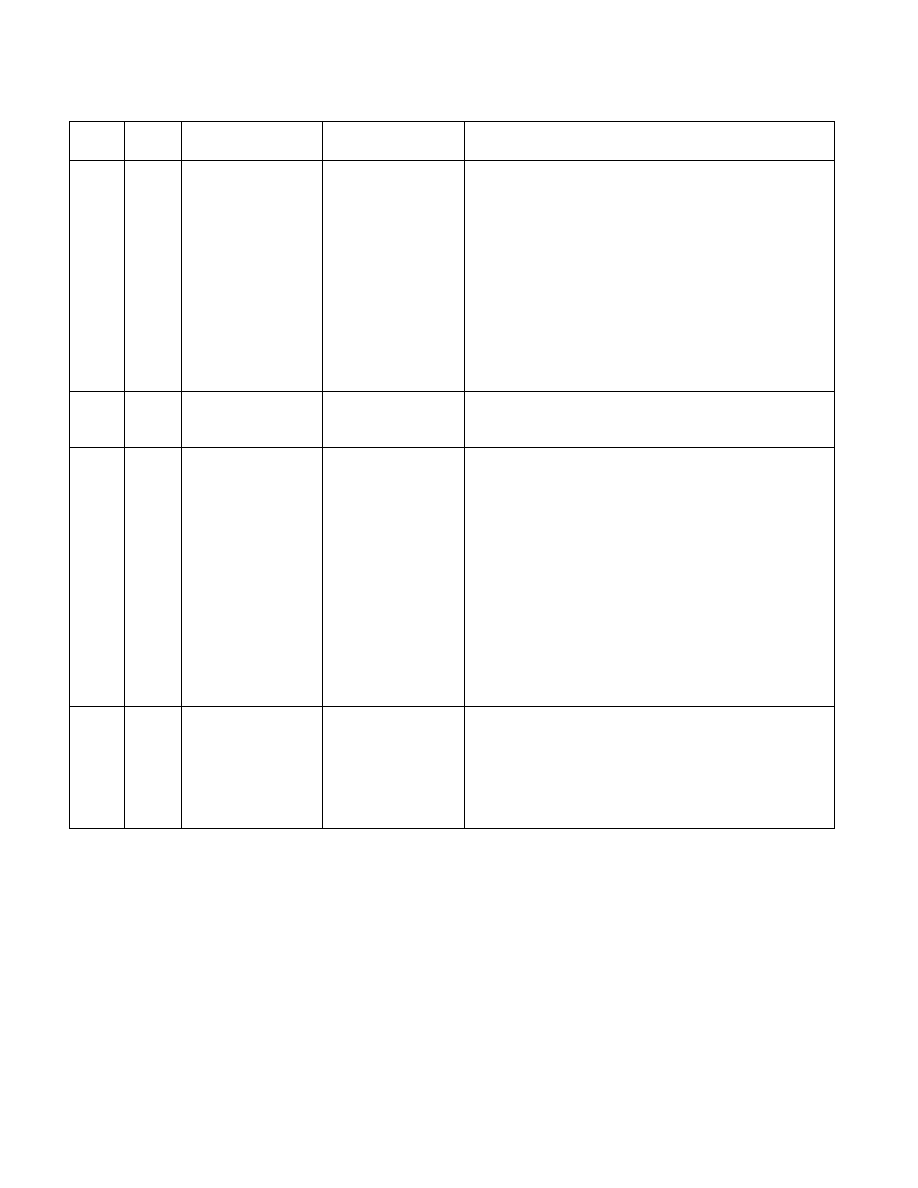

19-158 Vol. 3B

PERFORMANCE-MONITORING EVENTS

30H

See

and

L2_REJECT_BUSQ

Rejected L2 cache

requests.

This event indicates that a pending L2 cache request that

requires a bus transaction is delayed from moving to the bus

queue. Some of the reasons for this event are:

- The bus queue is full.

- The bus queue already holds an entry for a cache line in the

same set.

The number of events is greater or equal to the number of

requests that were rejected.

- For this core or both cores.

- Due to demand requests and L2 hardware prefetch requests

together, or separately.

- Of accesses to cache lines at different MESI states.

32H

See

L2_NO_REQ

Cycles no L2 cache

requests are pending.

This event counts the number of cycles that no L2 cache

requests are pending.

3AH

00H

EIST_TRANS

Number of Enhanced

Intel SpeedStep(R)

Technology (EIST)

transitions.

This event counts the number of Enhanced Intel SpeedStep(R)

Technology (EIST) transitions that include a frequency change,

either with or without VID change. This event is incremented

only while the counting core is in C0 state. In situations where

an EIST transition was caused by hardware as a result of CxE

state transitions, those EIST transitions will also be registered

in this event.

Enhanced Intel Speedstep Technology transitions are commonly

initiated by OS, but can be initiated by HW internally. For

example: CxE states are C-states (C1,C2,C3…) which not only

place the CPU into a sleep state by turning off the clock and

other components, but also lower the voltage (which reduces

the leakage power consumption). The same is true for thermal

throttling transition which uses Enhanced Intel Speedstep

Technology internally.

3BH

C0H

THERMAL_TRIP

Number of thermal

trips.

This event counts the number of thermal trips. A thermal trip

occurs whenever the processor temperature exceeds the

thermal trip threshold temperature. Following a thermal trip,

the processor automatically reduces frequency and voltage.

The processor checks the temperature every millisecond, and

returns to normal when the temperature falls below the

thermal trip threshold temperature.

Table 19-26. Non-Architectural Performance Events for 45 nm, 32 nm Intel® Atom™ Processors (Contd.)

Event

Num.

Umask

Value

Event Name

Definition

Description and Comment