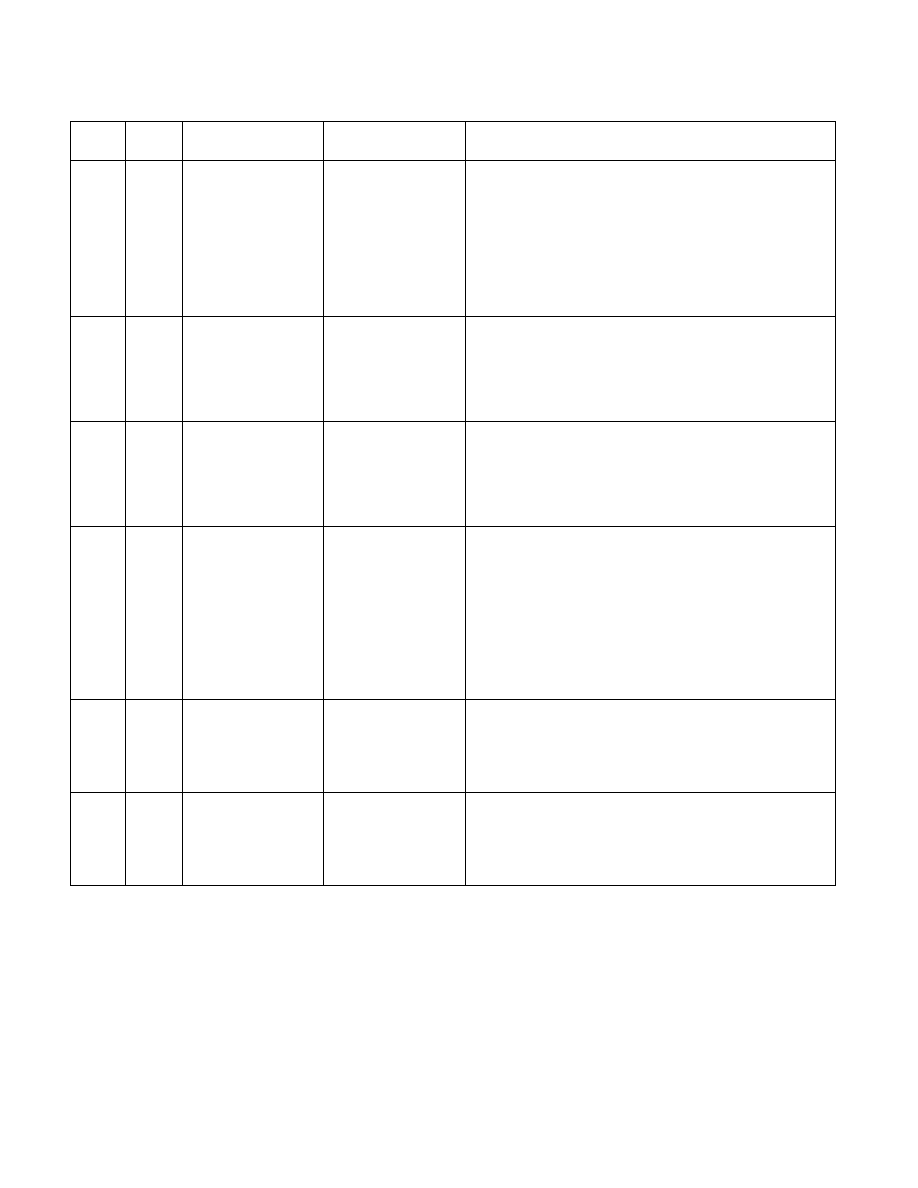

Vol. 3B 19-157

PERFORMANCE-MONITORING EVENTS

29H

See

and

L2_LD

L2 cache reads.

This event counts L2 cache read requests coming from the L1

data cache and L2 prefetchers.

This event can count occurrences for this core or both cores.

This event can count occurrences

- for this core or both cores.

- due to demand requests and L2 hardware prefetch requests

together or separately.

- of accesses to cache lines at different MESI states.

2AH

See

and

L2_ST

L2 store requests.

This event counts all store operations that miss the L1 data

cache and request the data from the L2 cache.

This event can count occurrences for this core or both cores.

This event can also count accesses to cache lines at different

MESI states.

2BH

See

and

L2_LOCK

L2 locked accesses.

This event counts all locked accesses to cache lines that miss

the L1 data cache.

This event can count occurrences for this core or both cores.

This event can also count accesses to cache lines at different

MESI states.

2EH

See

and

L2_RQSTS

L2 cache requests.

This event counts all completed L2 cache requests. This

includes L1 data cache reads, writes, and locked accesses, L1

data prefetch requests, instruction fetches, and all L2 hardware

prefetch requests.

This event can count occurrences

- for this core or both cores.

- due to demand requests and L2 hardware prefetch requests

together, or separately.

- of accesses to cache lines at different MESI states.

2EH

41H

L2_RQSTS.SELF.DEMA

ND.I_STATE

L2 cache demand

requests from this core

that missed the L2.

This event counts all completed L2 cache demand requests

from this core that miss the L2 cache. This includes L1 data

cache reads, writes, and locked accesses, L1 data prefetch

requests, and instruction fetches.

This is an architectural performance event.

2EH

4FH

L2_RQSTS.SELF.DEMA

ND.MESI

L2 cache demand

requests from this

core.

This event counts all completed L2 cache demand requests

from this core. This includes L1 data cache reads, writes, and

locked accesses, L1 data prefetch requests, and instruction

fetches.

This is an architectural performance event.

Table 19-26. Non-Architectural Performance Events for 45 nm, 32 nm Intel® Atom™ Processors (Contd.)

Event

Num.

Umask

Value

Event Name

Definition

Description and Comment