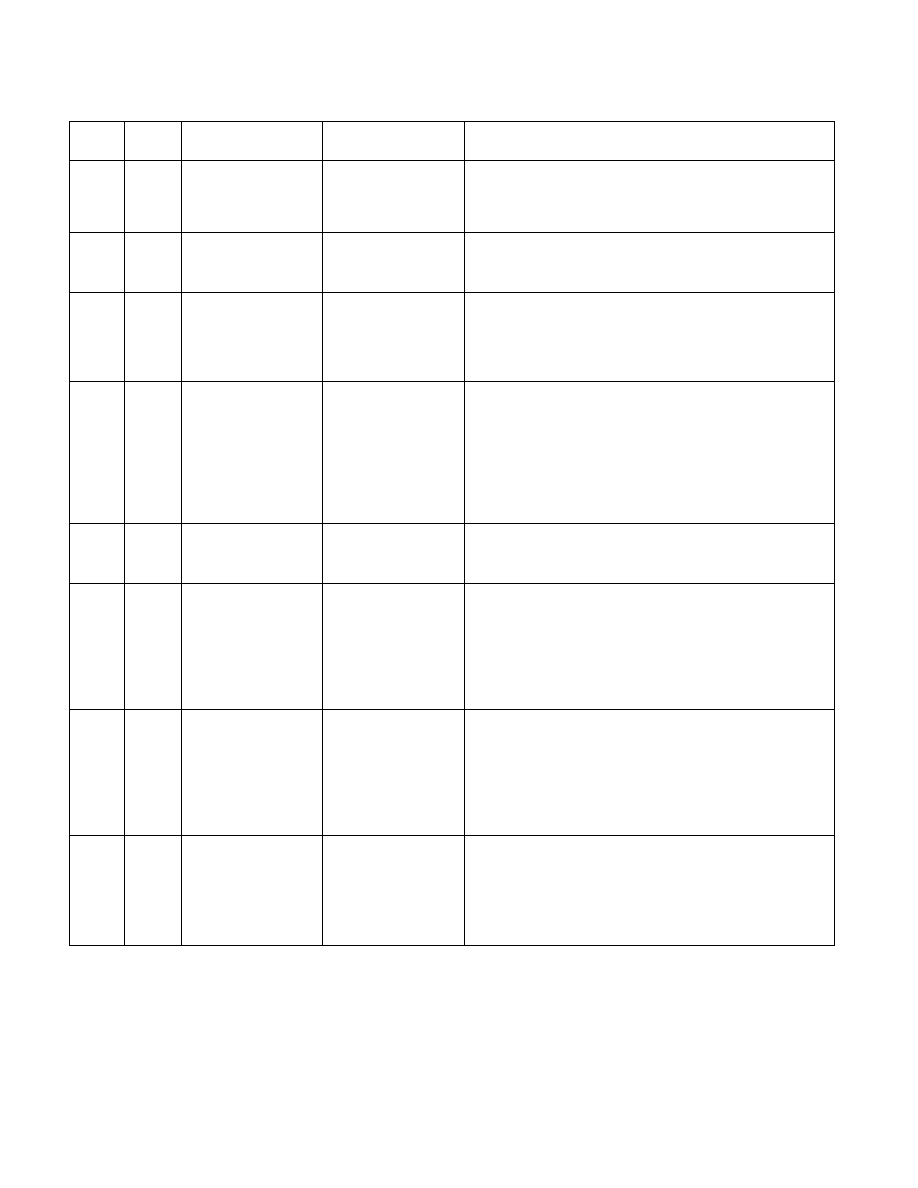

19-156 Vol. 3B

PERFORMANCE-MONITORING EVENTS

14H

01H

CYCLES_DIV_BUSY

Cycles the driver is

busy.

This event counts the number of cycles the divider is busy

executing divide or square root operations. The divide can be

integer, X87 or Streaming SIMD Extensions (SSE). The square

root operation can be either X87 or SSE.

21H

See

L2_ADS

Cycles L2 address bus

is in use.

This event counts the number of cycles the L2 address bus is

being used for accesses to the L2 cache or bus queue.

This event can count occurrences for this core or both cores.

22H

See

L2_DBUS_BUSY

Cycles the L2 cache

data bus is busy.

This event counts core cycles during which the L2 cache data

bus is busy transferring data from the L2 cache to the core. It

counts for all L1 cache misses (data and instruction) that hit the

L2 cache. The count will increment by two for a full cache-line

request.

24H

See

and

L2_LINES_IN

L2 cache misses.

This event counts the number of cache lines allocated in the L2

cache. Cache lines are allocated in the L2 cache as a result of

requests from the L1 data and instruction caches and the L2

hardware prefetchers to cache lines that are missing in the L2

cache.

This event can count occurrences for this core or both cores.

This event can also count demand requests and L2 hardware

prefetch requests together or separately.

25H

See

L2_M_LINES_IN

L2 cache line

modifications.

This event counts whenever a modified cache line is written

back from the L1 data cache to the L2 cache.

This event can count occurrences for this core or both cores.

26H

See

and

L2_LINES_OUT

L2 cache lines evicted. This event counts the number of L2 cache lines evicted.

This event can count occurrences for this core or both cores.

This event can also count evictions due to demand requests and

L2 hardware prefetch requests together or separately.

27H

See

and

L2_M_LINES_OUT

Modified lines evicted

from the L2 cache.

This event counts the number of L2 modified cache lines

evicted. These lines are written back to memory unless they

also exist in a shared-state in one of the L1 data caches.

This event can count occurrences for this core or both cores.

This event can also count evictions due to demand requests and

L2 hardware prefetch requests together or separately.

28H

See

and

L2_IFETCH

L2 cacheable

instruction fetch

requests.

This event counts the number of instruction cache line requests

from the ICache. It does not include fetch requests from

uncacheable memory. It does not include ITLB miss accesses.

This event can count occurrences for this core or both cores.

This event can also count accesses to cache lines at different

MESI states.

Table 19-26. Non-Architectural Performance Events for 45 nm, 32 nm Intel® Atom™ Processors (Contd.)

Event

Num.

Umask

Value

Event Name

Definition

Description and Comment