Vol. 3B 19-149

PERFORMANCE-MONITORING EVENTS

19.12 PERFORMANCE MONITORING EVENTS FOR PROCESSORS BASED ON THE

SILVERMONT MICROARCHITECTURE

Processors based on the Silvermont microarchitecture support the architectural performance-monitoring events

listed in Table 19-1 and fixed-function performance events using fixed counter. In addition, they also support the

following non-architectural performance-monitoring events listed in Table 19-25. These processors have the CPUID

signatures of 06_37H, 06_4AH, 06_4DH, 06_5AH, and 06_5DH.

Performance monitoring event descriptions may refer to terminology described in Section B.2, “Intel® Xeon®

processor 5500 Series,” in Appendix B of the Intel® 64 and IA-32 Architectures Optimization Reference Manual.

E6H

01H

BACLEARS.ALL

Counts the number of times a BACLEAR is signaled for any reason,

including, but not limited to indirect branch/call, Jcc (Jump on Conditional

Code/Jump if Condition is Met) branch, unconditional branch/call, and

returns.

E6H

08H

BACLEARS.RETURN

Counts BACLEARS on return instructions.

E6H

10H

BACLEARS.COND

Counts BACLEARS on Jcc (Jump on Conditional Code/Jump if Condition is

Met) branches.

E7H

01H

MS_DECODED.MS_ENTR

Y

Counts the number of times the Microcode Sequencer (MS) starts a

flow of uops from the MSROM. It does not count every time a uop is

read from the MSROM. The most common case that this counts is when

a micro-coded instruction is encountered by the front end of the

machine. Other cases include when an instruction encounters a fault,

trap, or microcode assist of any sort that initiates a flow of uops. The

event will count MS startups for uops that are speculative, and

subsequently cleared by branch mispredict or a machine clear.

E9H

01H

DECODE_RESTRICTION.

PREDECODE_WRONG

Counts the number of times the prediction (from the pre-decode cache)

for instruction length is incorrect.

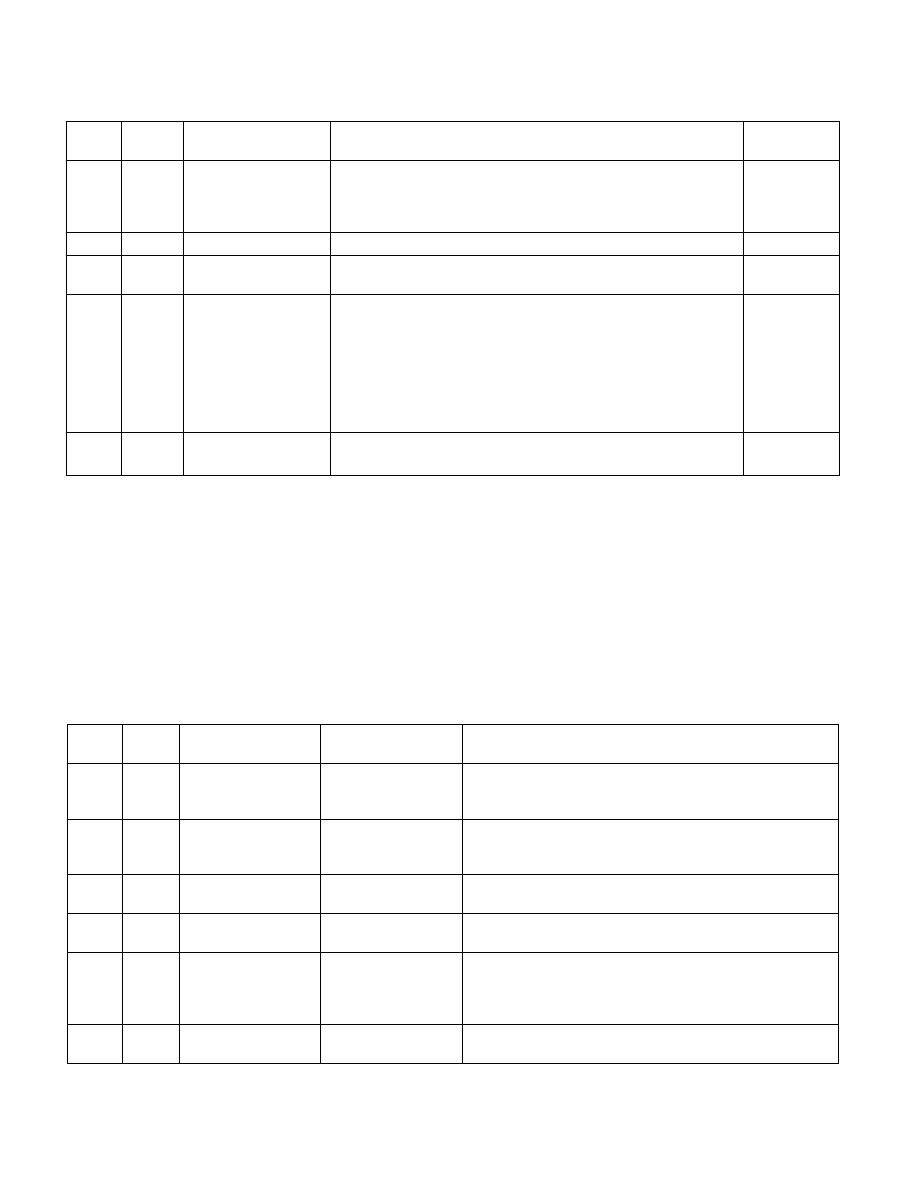

Table 19-25. Performance Events for Silvermont Microarchitecture

Event

Num.

Umask

Value

Event Name

Definition

Description and Comment

03

H

01

H

REHABQ.LD_BLOCK_S

T_FORWARD

Loads blocked due to

store forward

restriction.

This event counts the number of retired loads that were

prohibited from receiving forwarded data from the store

because of address mismatch.

03

H

02

H

REHABQ.LD_BLOCK_S

TD_NOTREADY

Loads blocked due to

store data not ready.

This event counts the cases where a forward was technically

possible, but did not occur because the store data was not

available at the right time.

03

H

04

H

REHABQ.ST_SPLITS

Store uops that split

cache line boundary.

This event counts the number of retire stores that experienced

cache line boundary splits.

03

H

08

H

REHABQ.LD_SPLITS

Load uops that split

cache line boundary.

This event counts the number of retire loads that experienced

cache line boundary splits.

03

H

10

H

REHABQ.LOCK

Uops with lock

semantics.

This event counts the number of retired memory operations

with lock semantics. These are either implicit locked instructions

such as the XCHG instruction or instructions with an explicit

LOCK prefix (F0H).

03

H

20

H

REHABQ.STA_FULL

Store address buffer

full.

This event counts the number of retired stores that are delayed

because there is not a store address buffer available.

Table 19-24. Non-Architectural Performance Events for the Goldmont Microarchitecture (Contd.)

Event

Num.

Umask

Value

Event Name

Description

Comment