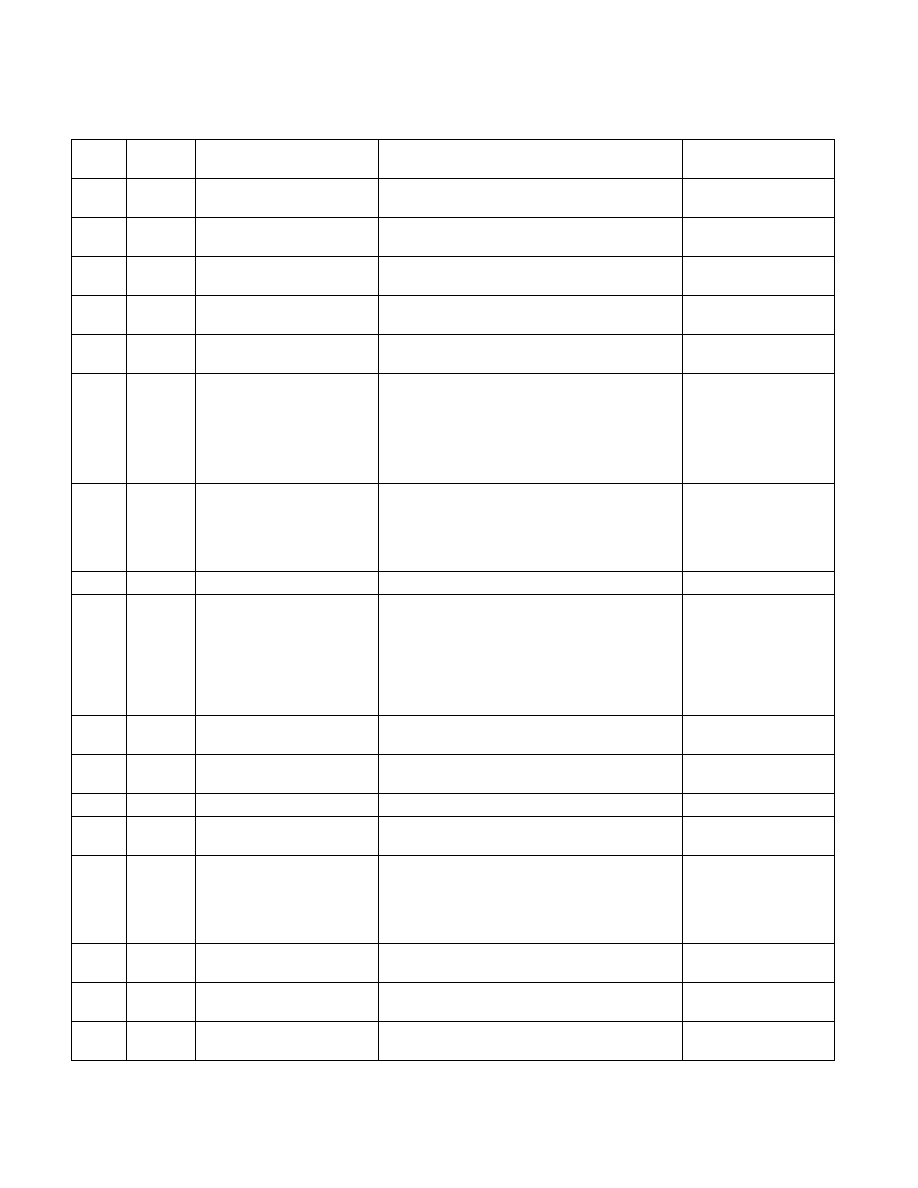

Vol. 3B 19-97

PERFORMANCE-MONITORING EVENTS

B7H

01H

OFF_CORE_RESPONSE_0

See Section 18.8.1.3, “Off-core Response

Performance Monitoring in the Processor Core”.

Requires programming

MSR 01A6H.

B8H

01H

SNOOP_RESPONSE.HIT

Counts HIT snoop response sent by this thread in

response to a snoop request.

B8H

02H

SNOOP_RESPONSE.HITE

Counts HIT E snoop response sent by this thread in

response to a snoop request.

B8H

04H

SNOOP_RESPONSE.HITM

Counts HIT M snoop response sent by this thread in

response to a snoop request.

BBH

01H

OFF_CORE_RESPONSE_1

See Section 18.8.1.3, “Off-core Response

Performance Monitoring in the Processor Core”.

Use MSR 01A7H.

C0H

00H

INST_RETIRED.ANY_P

See Table 19-1.

Notes: INST_RETIRED.ANY is counted by a

designated fixed counter. INST_RETIRED.ANY_P is

counted by a programmable counter and is an

architectural performance event. Event is

supported if CPUID.A.EBX[1] = 0.

Counting: Faulting

executions of

GETSEC/VM entry/VM

Exit/MWait will not count

as retired instructions.

C0H

02H

INST_RETIRED.X87

Counts the number of floating point computational

operations retired: floating point computational

operations executed by the assist handler and sub-

operations of complex floating point instructions

like transcendental instructions.

C0H

04H

INST_RETIRED.MMX

Counts the number of retired: MMX instructions.

C2H

01H

UOPS_RETIRED.ANY

Counts the number of micro-ops retired, (macro-

fused=1, micro-fused=2, others=1; maximum count

of 8 per cycle). Most instructions are composed of

one or two micro-ops. Some instructions are

decoded into longer sequences such as repeat

instructions, floating point transcendental

instructions, and assists.

Use cmask=1 and invert

to count active cycles or

stalled cycles.

C2H

02H

UOPS_RETIRED.RETIRE_SLOT

S

Counts the number of retirement slots used each

cycle.

C2H

04H

UOPS_RETIRED.MACRO_FUSE

D

Counts number of macro-fused uops retired.

C3H

01H

MACHINE_CLEARS.CYCLES

Counts the cycles machine clear is asserted.

C3H

02H

MACHINE_CLEARS.MEM_ORDE

R

Counts the number of machine clears due to

memory order conflicts.

C3H

04H

MACHINE_CLEARS.SMC

Counts the number of times that a program writes

to a code section. Self-modifying code causes a

severe penalty in all Intel 64 and IA-32 processors.

The modified cache line is written back to the L2

and L3caches.

C4H

00H

BR_INST_RETIRED.ALL_BRAN

CHES

Branch instructions at retirement.

See Table 19-1.

C4H

01H

BR_INST_RETIRED.CONDITION

AL

Counts the number of conditional branch

instructions retired.

C4H

02H

BR_INST_RETIRED.NEAR_CAL

L

Counts the number of direct & indirect near

unconditional calls retired.

Table 19-19. Non-Architectural Performance Events In the Processor Core for

Processors Based on Intel® Microarchitecture Code Name Westmere (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment