Vol. 3B 19-85

PERFORMANCE-MONITORING EVENTS

Intel Xeon processors with CPUID signature of DisplayFamily_DisplayModel 06_2EH have a distinct uncore sub-

system that is significantly different from the uncore found in processors with CPUID signature 06_1AH, 06_1EH,

and 06_1FH. Non-architectural Performance monitoring events for its uncore will be available in future documen-

tation.

19.8

PERFORMANCE MONITORING EVENTS FOR PROCESSORS BASED ON

INTEL

®

MICROARCHITECTURE CODE NAME WESTMERE

Intel 64 processors based on Intel

®

microarchitecture code name Westmere support the architectural and non-

architectural performance-monitoring events listed in Table 19-1 and Table 19-19. Table 19-19 applies to proces-

sors with CPUID signature of DisplayFamily_DisplayModel encoding with the following values: 06_25H, 06_2CH. In

addition, these processors (CPUID signature of DisplayFamily_DisplayModel 06_25H, 06_2CH) also support the

following non-architectural, product-specific uncore performance-monitoring events listed in Table 19-20. Fixed

counters support the architecture events defined in Table 19-2.

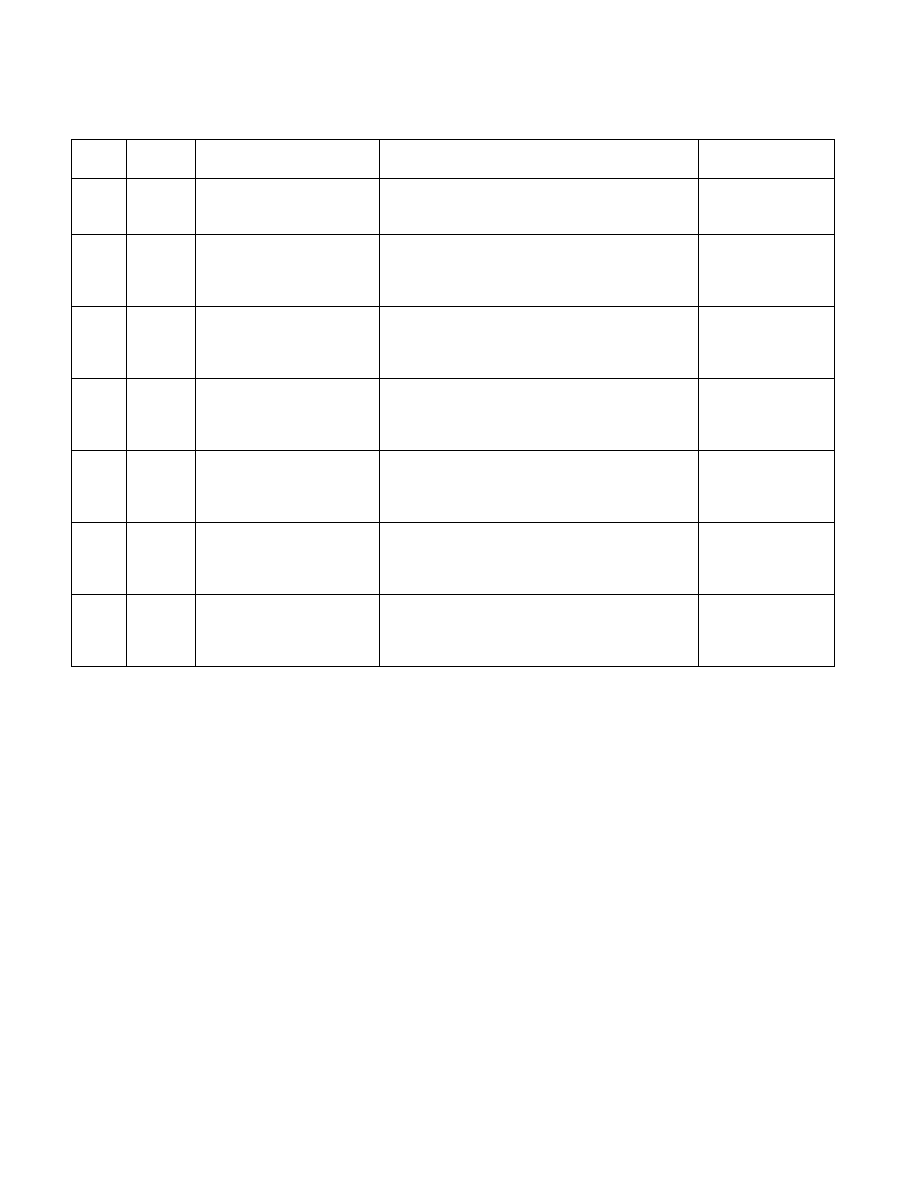

64H

20H

UNC_DRAM_WRITE_CAS.AUTO

PRE_CH2

Counts the number of times a write CAS command was

issued on DRAM channel 2 where the command issued

used the auto-precharge (auto page close) mode.

65H

01H

UNC_DRAM_REFRESH.CH0

Counts number of DRAM channel 0 refresh commands.

DRAM loses data content over time. In order to keep

correct data content, the data values have to be

refreshed periodically.

65H

02H

UNC_DRAM_REFRESH.CH1

Counts number of DRAM channel 1 refresh commands.

DRAM loses data content over time. In order to keep

correct data content, the data values have to be

refreshed periodically.

65H

04H

UNC_DRAM_REFRESH.CH2

Counts number of DRAM channel 2 refresh commands.

DRAM loses data content over time. In order to keep

correct data content, the data values have to be

refreshed periodically.

66H

01H

UNC_DRAM_PRE_ALL.CH0

Counts number of DRAM Channel 0 precharge-all

(PREALL) commands that close all open pages in a

rank. PREALL is issued when the DRAM needs to be

refreshed or needs to go into a power down mode.

66H

02H

UNC_DRAM_PRE_ALL.CH1

Counts number of DRAM Channel 1 precharge-all

(PREALL) commands that close all open pages in a

rank. PREALL is issued when the DRAM needs to be

refreshed or needs to go into a power down mode.

66H

04H

UNC_DRAM_PRE_ALL.CH2

Counts number of DRAM Channel 2 precharge-all

(PREALL) commands that close all open pages in a

rank. PREALL is issued when the DRAM needs to be

refreshed or needs to go into a power down mode.

Table 19-18. Non-Architectural Performance Events In the Processor Uncore for

Intel® Core™ i7 Processor and Intel® Xeon® Processor 5500 Series (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment