19-68 Vol. 3B

PERFORMANCE-MONITORING EVENTS

B0H

40H

OFFCORE_REQUESTS.L1D_WR

ITEBACK

Counts number of L1D writebacks to the uncore.

B1H

01H

UOPS_EXECUTED.PORT0

Counts number of uops executed that were issued

on port 0. Port 0 handles integer arithmetic, SIMD

and FP add uops.

B1H

02H

UOPS_EXECUTED.PORT1

Counts number of uops executed that were issued

on port 1. Port 1 handles integer arithmetic, SIMD,

integer shift, FP multiply and FP divide uops.

B1H

04H

UOPS_EXECUTED.PORT2_COR

E

Counts number of uops executed that were issued

on port 2. Port 2 handles the load uops. This is a

core count only and cannot be collected per thread.

B1H

08H

UOPS_EXECUTED.PORT3_COR

E

Counts number of uops executed that were issued

on port 3. Port 3 handles store uops. This is a core

count only and cannot be collected per thread.

B1H

10H

UOPS_EXECUTED.PORT4_COR

E

Counts number of uops executed that where issued

on port 4. Port 4 handles the value to be stored for

the store uops issued on port 3. This is a core count

only and cannot be collected per thread.

B1H

1FH

UOPS_EXECUTED.CORE_ACTIV

E_CYCLES_NO_PORT5

Counts cycles when the uops executed were issued

from any ports except port 5. Use Cmask=1 for

active cycles; Cmask=0 for weighted cycles. Use

CMask=1, Invert=1 to count P0-4 stalled cycles. Use

Cmask=1, Edge=1, Invert=1 to count P0-4 stalls.

B1H

20H

UOPS_EXECUTED.PORT5

Counts number of uops executed that where issued

on port 5.

B1H

3FH

UOPS_EXECUTED.CORE_ACTIV

E_CYCLES

Counts cycles when the uops are executing. Use

Cmask=1 for active cycles; Cmask=0 for weighted

cycles. Use CMask=1, Invert=1 to count P0-4 stalled

cycles. Use Cmask=1, Edge=1, Invert=1 to count P0-

4 stalls.

B1H

40H

UOPS_EXECUTED.PORT015

Counts number of uops executed that where issued

on port 0, 1, or 5.

Use cmask=1, invert=1

to count stall cycles.

B1H

80H

UOPS_EXECUTED.PORT234

Counts number of uops executed that where issued

on port 2, 3, or 4.

B2H

01H

OFFCORE_REQUESTS_SQ_FUL

L

Counts number of cycles the SQ is full to handle off-

core requests.

B7H

01H

OFF_CORE_RESPONSE_0

See Section 18.8.1.3, “Off-core Response

Performance Monitoring in the Processor Core”.

Requires programming

MSR 01A6H.

B8H

01H

SNOOP_RESPONSE.HIT

Counts HIT snoop response sent by this thread in

response to a snoop request.

B8H

02H

SNOOP_RESPONSE.HITE

Counts HIT E snoop response sent by this thread in

response to a snoop request.

B8H

04H

SNOOP_RESPONSE.HITM

Counts HIT M snoop response sent by this thread in

response to a snoop request.

BBH

01H

OFF_CORE_RESPONSE_1

See Section 18.8.4, “Performance Monitoring for

Requires programming

MSR 01A7H.

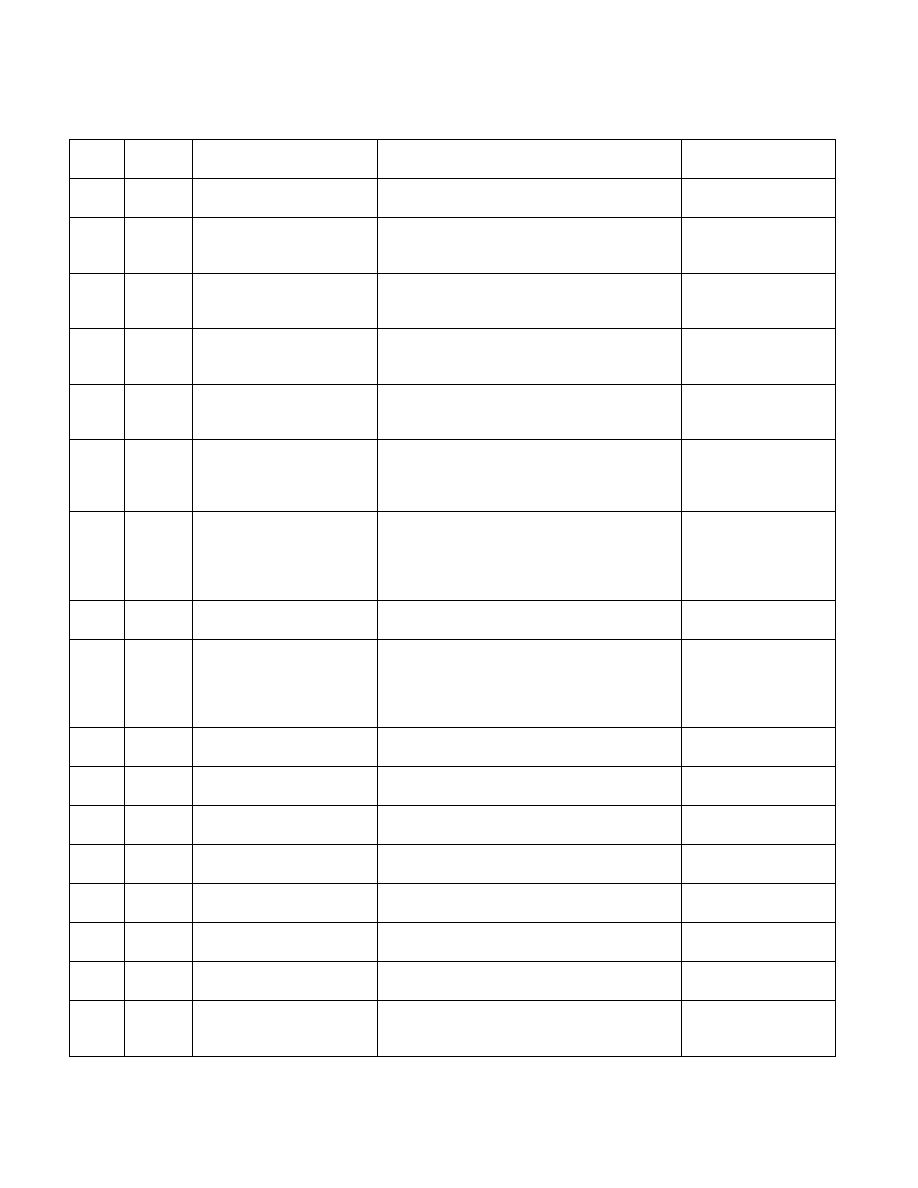

Table 19-17. Non-Architectural Performance Events In the Processor Core for

Intel® Core™ i7 Processor and Intel® Xeon® Processor 5500 Series (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment