18-110 Vol. 3B

PERFORMANCE MONITORING

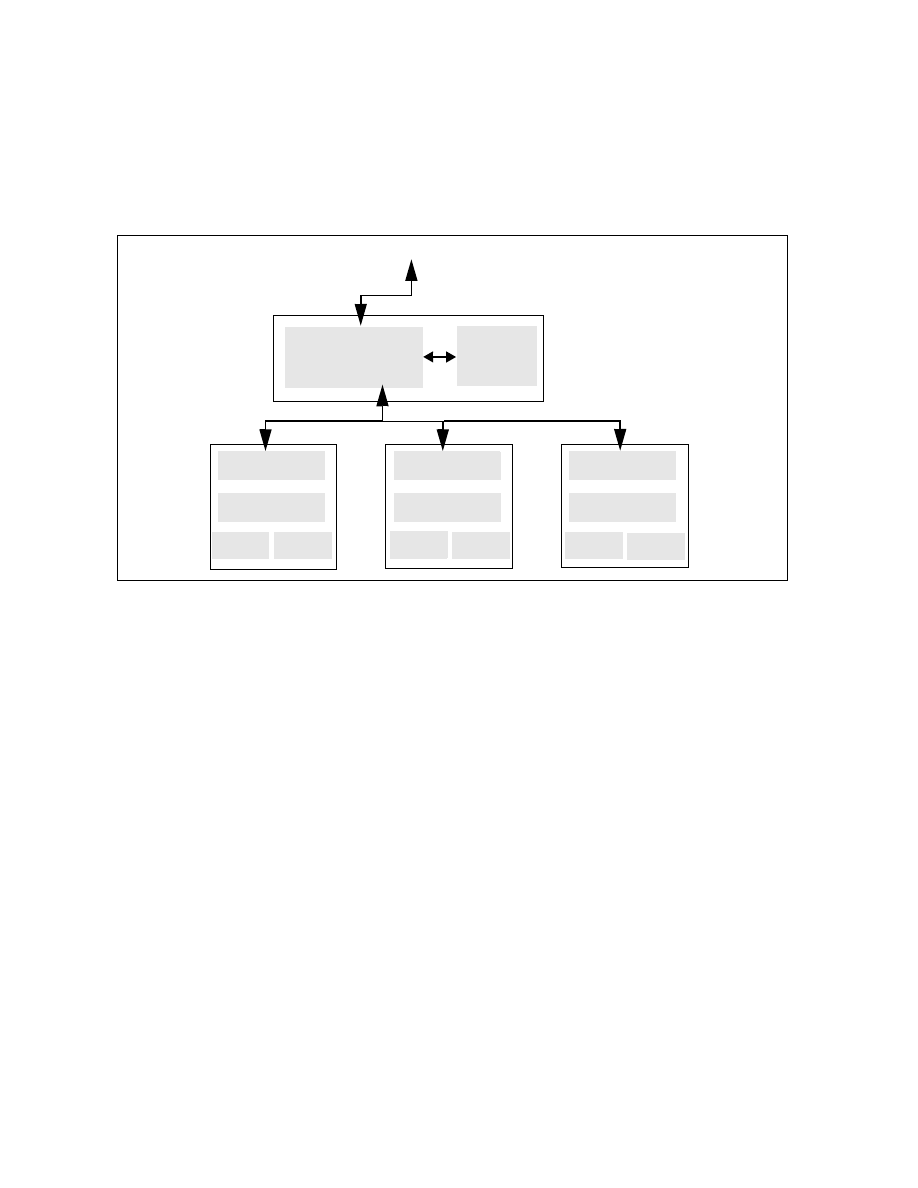

provides three Simple Direct Interface (SDI) to service transactions originated the XQ-replacement SDI logic in

each dual-core modules. In Intel Xeon processor 7100 series, the IOQ logic in each processor core is replaced with

a Simple Direct Interface (SDI) logic. The L3 cache is connected between the system bus and the SDI through addi-

tional control logic. See Figure 18-55 for the block configuration of six processor cores and the L3/Caching bus

controller sub-system in Intel Xeon processor 7400 series. Figure 18-55 shows the block configuration of two

processor cores (four logical processors) and the L3/Caching bus controller sub-system in Intel Xeon processor

7100 series.

Almost all of the performance monitoring capabilities available to processor cores with the same CPUID signatures

(see Section 18.1 and Section 18.16) apply to Intel Xeon processor 7100 series. The MSRs used by performance

monitoring interface are shared between two logical processors in the same processor core.

The performance monitoring capabilities available to processor with DisplayFamily_DisplayModel signature 06_17H

also apply to Intel Xeon processor 7400 series. Each processor core provides its own set of MSRs for performance

monitoring interface.

The IOQ_allocation and IOQ_active_entries events are not supported in Intel Xeon processor 7100 series and 7400

series. Additional performance monitoring capabilities applicable to the L3/caching bus controller sub-system are

described in this section.

Figure 18-55. Block Diagram of Intel Xeon Processor 7400 Series

SDI interface

L2

SDI interface

L2

L3

GBSQ, GSNPQ,

GINTQ, ...

FSB

SDI

SDI interface

L2

Core

Core

Core

Core

Core

Core