Vol. 3B 18-109

PERFORMANCE MONITORING

•

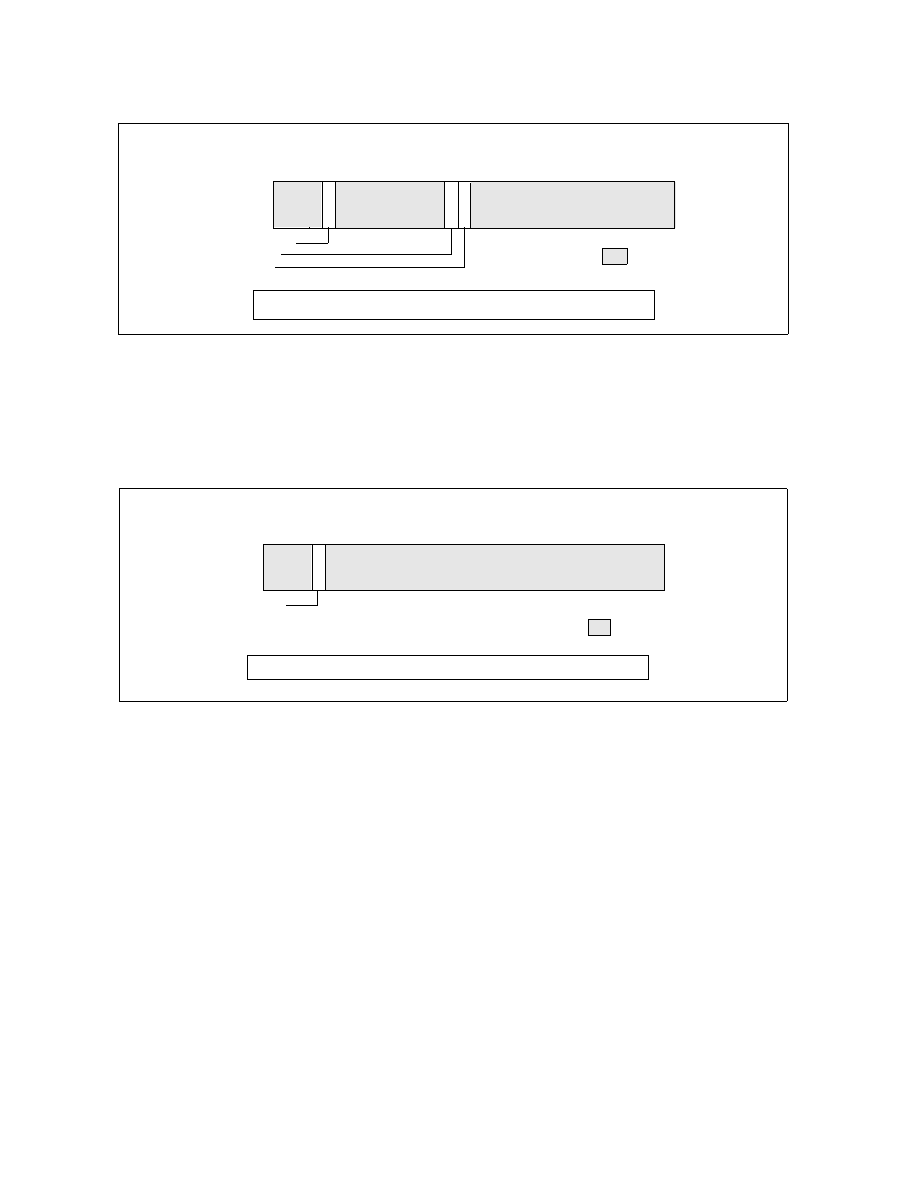

IBUSQ Latency event — This event accumulates weighted cycle counts for latency measurement of transac-

tions in the iBUSQ unit. The count is enabled by setting MSR_IFSB_CTRL6[bit 26] to 1; the count freezes after

software sets MSR_IFSB_CTRL6[bit 26] to 0. MSR_IFSB_CNTR7 acts as a 64-bit event counter for this event.

See Figure 18-54.

18.21 PERFORMANCE MONITORING ON L3 AND CACHING BUS CONTROLLER

SUB-SYSTEMS

The Intel Xeon processor 7400 series and Dual-Core Intel Xeon processor 7100 series employ a distinct L3/caching

bus controller sub-system. These sub-system have a unique set of performance monitoring capability and

programming interfaces that are largely common between these two processor families.

Intel Xeon processor 7400 series are based on 45 nm enhanced Intel Core microarchitecture. The CPUID signature

is indicated by DisplayFamily_DisplayModel value of 06_1DH (see CPUID instruction in Chapter 3, “Instruction Set

Reference, A-L” in the Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 2A). Intel Xeon

processor 7400 series have six processor cores that share an L3 cache.

Dual-Core Intel Xeon processor 7100 series are based on Intel NetBurst microarchitecture, have a CPUID signature

of family [0FH], model [06H] and a unified L3 cache shared between two cores. Each core in an Intel Xeon

processor 7100 series supports Intel Hyper-Threading Technology, providing two logical processors per core.

Both Intel Xeon processor 7400 series and Intel Xeon processor 7100 series support multi-processor configurations

using system bus interfaces. In Intel Xeon processor 7400 series, the L3/caching bus controller sub-system

Figure 18-53. MSR_EFSB_DRDYx, Addresses: 107D0H and 107D1H

Figure 18-54. MSR_IFSB_CTL6, Address: 107D2H;

MSR_IFSB_CNTR7, Address: 107D3H

Other

49

38

50

37 36

33

34

Saturate

Own

Reserved

63

56 55

48

32

57

58

59

60

35

39

31

0

32 bit event count

MSR_EFSB_DRDYx, Addresses: 107D0H and 107D1H

Reserved

MSR_IFSB_CTL6 Address: 107D2H

MSR_IFSB_CNTR7 Address: 107D3H

Enable

63

0

57

59

63

0

64 bit event count