Vol. 3B 18-103

PERFORMANCE MONITORING

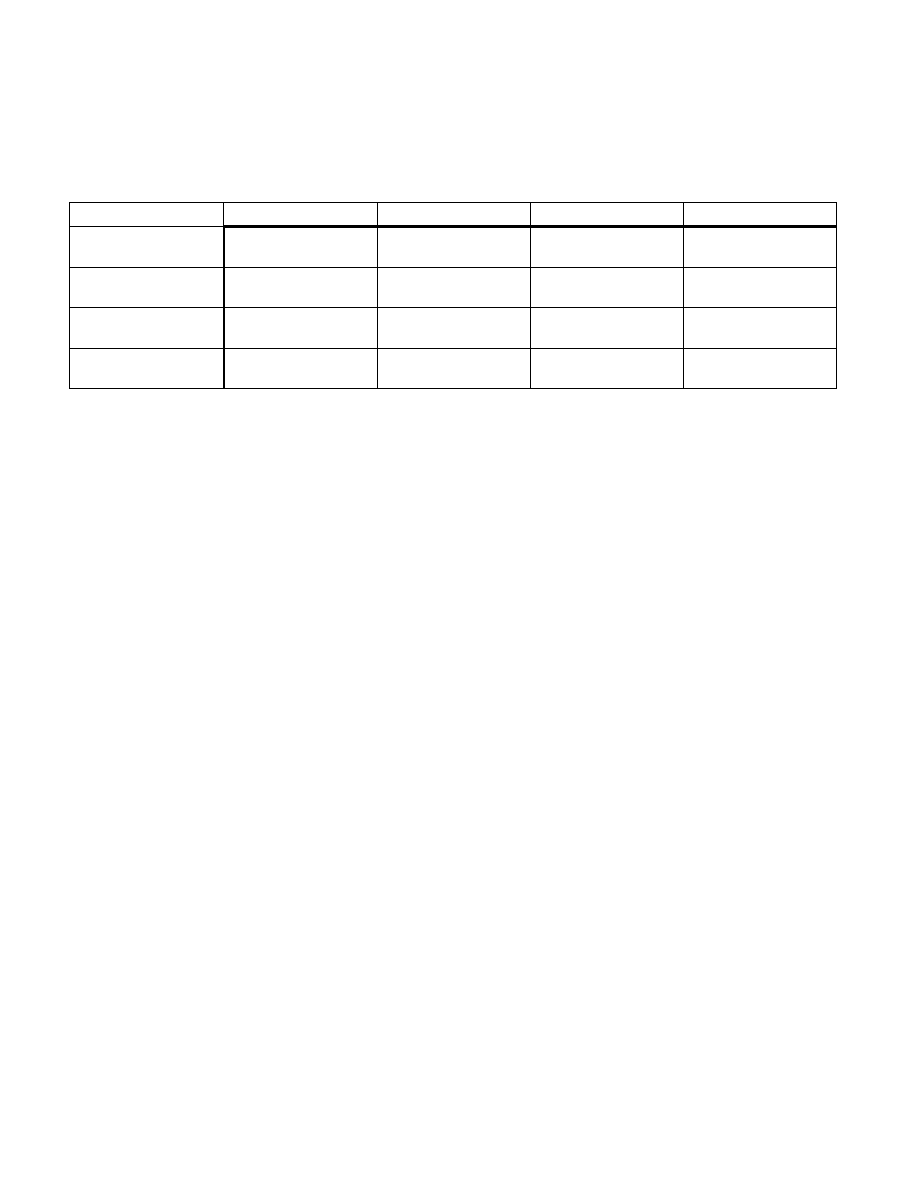

When a bit in the event mask field is TI, the effect of specifying bit-0-3 of the associated ESCR are described in

Table 15-6. For events that are marked as TI in Chapter 19, the effect of selectively specifying T0_USR, T0_OS,

T1_USR, T1_OS bits is shown in Table 18-67.

18.17 COUNTING

CLOCKS

The count of cycles, also known as clockticks, forms a the basis for measuring how long a program takes to

execute. Clockticks are also used as part of efficiency ratios like cycles per instruction (CPI). Processor clocks may

stop ticking under circumstances like the following:

•

The processor is halted when there is nothing for the CPU to do. For example, the processor may halt to save

power while the computer is servicing an I/O request. When Intel Hyper-Threading Technology is enabled, both

logical processors must be halted for performance-monitoring counters to be powered down.

•

The processor is asleep as a result of being halted or because of a power-management scheme. There are

different levels of sleep. In the some deep sleep levels, the time-stamp counter stops counting.

In addition, processor core clocks may undergo transitions at different ratios relative to the processor’s bus clock

frequency. Some of the situations that can cause processor core clock to undergo frequency transitions include:

•

TM2 transitions

•

Enhanced Intel SpeedStep Technology transitions (P-state transitions)

For Intel processors that support Intel Dynamic Acceleration or XE operation, the processor core clocks may

operate at a frequency that differs from the Processor Base frequency (as indicated by processor frequency infor-

mation reported by CPUID instruction). See Section 18.17.5 for more detail.

There are several ways to count processor clock cycles to monitor performance. These are:

•

Non-halted clockticks — Measures clock cycles in which the specified logical processor is not halted and is

not in any power-saving state. When Intel Hyper-Threading Technology is enabled, ticks can be measured on a

per-logical-processor basis. There are also performance events on dual-core processors that measure

clockticks per logical processor when the processor is not halted.

•

Non-sleep clockticks — Measures clock cycles in which the specified physical processor is not in a sleep mode

or in a power-saving state. These ticks cannot be measured on a logical-processor basis.

•

Time-stamp counter — Measures clock cycles in which the physical processor is not in deep sleep. These ticks

cannot be measured on a logical-processor basis.

•

Reference clockticks — TM2 or Enhanced Intel SpeedStep technology are two examples of processor

features that can cause processor core clockticks to represent non-uniform tick intervals due to change of bus

ratios. Performance events that counts clockticks of a constant reference frequency was introduced Intel Core

Duo and Intel Core Solo processors. The mechanism is further enhanced on processors based on Intel Core

microarchitecture.

Some processor models permit clock cycles to be measured when the physical processor is not in deep sleep (by

using the time-stamp counter and the RDTSC instruction). Note that such ticks cannot be measured on a per-

logical-processor basis. See Section 17.15, “Time-Stamp Counter,” for detail on processor capabilities.

Table 18-67. Effect of Logical Processor and CPL Qualification

for Non-logical-Processor-specific (TI) Events

T1_OS/T1_USR = 00

T1_OS/T1_USR = 01

T1_OS/T1_USR = 11

T1_OS/T1_USR = 10

T0_OS/T0_USR = 00

Zero count

Counts while (a) T0 in

USR or (b) T1 in USR

Counts irrespective of

CPL, T0, T1

Counts while (a) T0 in OS

or (b) T1 in OS

T0_OS/T0_USR = 01

Counts while (a) T0 in

USR or (b) T1 in USR

Counts while (a) T0 in

USR or (b) T1 in USR

Counts irrespective of

CPL, T0, T1

Counts irrespective of

CPL, T0, T1

T0_OS/T0_USR = 11

Counts irrespective of

CPL, T0, T1

Counts irrespective of

CPL, T0, T1

Counts irrespective of

CPL, T0, T1

Counts irrespective of

CPL, T0, T1

T0_OS/T0_USR = 0

Counts while (a) T0 in OS

or (b) T1 in OS

Counts irrespective of

CPL, T0, T1

Counts irrespective of

CPL, T0, T1

Counts while (a) T0 in OS

or (b) T1 in OS