Vol. 3B 18-85

PERFORMANCE MONITORING

•

Interrupt-based event sampling — A performance counter is configured to count one or more types of

events and to generate an interrupt when it overflows. To trigger an overflow, the counter is preset to a

modulus value that will cause the counter to overflow after a specific number of events have been counted.

When the counter overflows, the processor generates a performance monitoring interrupt (PMI). The interrupt

service routine for the PMI then records the return instruction pointer (RIP), resets the modulus, and restarts

the counter. Code performance can be analyzed by examining the distribution of RIPs with a tool like the

VTune™ Performance Analyzer.

•

Processor event-based sampling (PEBS) — In PEBS, the processor writes a record of the architectural

state of the processor to a memory buffer after the counter overflows. The records of architectural state

provide additional information for use in performance tuning. Processor-based event sampling can be used to

count only a subset of at-retirement events. PEBS captures more precise processor state information compared

to interrupt based event sampling, because the latter need to use the interrupt service routine to re-construct

the architectural states of processor.

The following sections describe the MSRs and data structures used for performance monitoring in the Pentium 4

and Intel Xeon processors.

18.15.1 ESCR

MSRs

The 45 ESCR MSRs (see Table 18-63) allow software to select specific events to be countered. Each ESCR is usually

associated with a pair of performance counters (see Table 18-63) and each performance counter has several ESCRs

associated with it (allowing the events counted to be selected from a variety of events).

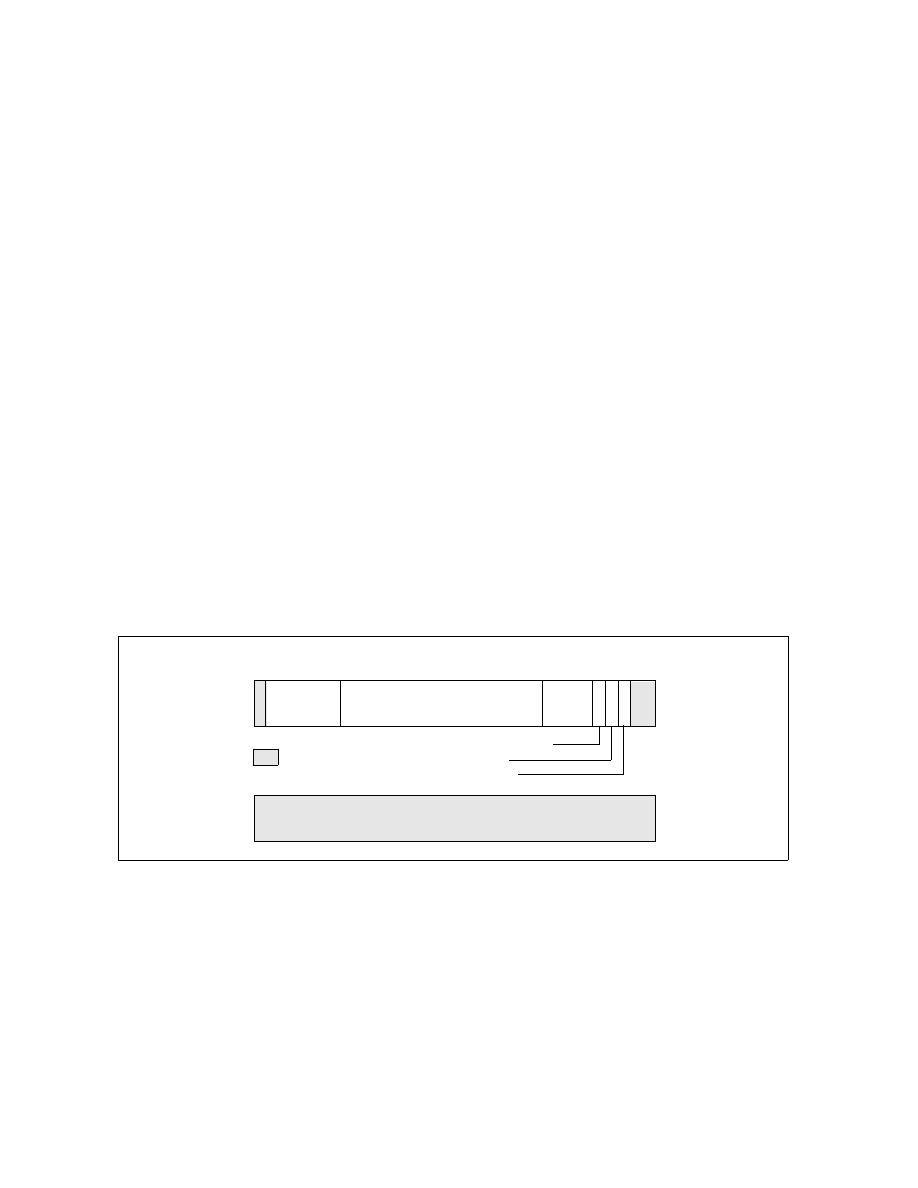

Figure 18-43 shows the layout of an ESCR MSR. The functions of the flags and fields are:

•

USR flag, bit 2 — When set, events are counted when the processor is operating at a current privilege level

(CPL) of 1, 2, or 3. These privilege levels are generally used by application code and unprotected operating

system code.

•

OS flag, bit 3 — When set, events are counted when the processor is operating at CPL of 0. This privilege level

is generally reserved for protected operating system code. (When both the OS and USR flags are set, events

are counted at all privilege levels.)

•

Tag enable, bit 4 — When set, enables tagging of μops to assist in at-retirement event counting; when clear,

disables tagging. See Section 18.15.6, “At-Retirement Counting.”

•

Tag value field, bits 5 through 8 — Selects a tag value to associate with a μop to assist in at-retirement

event counting.

•

Event mask field, bits 9 through 24 — Selects events to be counted from the event class selected with the

event select field.

•

Event select field, bits 25 through 30) — Selects a class of events to be counted. The events within this

class that are counted are selected with the event mask field.

Figure 18-43. Event Selection Control Register (ESCR) for Pentium 4

and Intel Xeon Processors without Intel HT Technology Support

31

24

8

0

1

2

3

4

9

25

30

63

32

Reserved

Event Mask

Event

Select

USR

OS

5

Tag Enable

Tag

Value

Reserved