Vol. 3B 18-33

PERFORMANCE MONITORING

To properly program this extra register, software must set at least one request type bit (Table 18-15) and a valid

response type pattern (either Table 18-16 or Table 18-22). Otherwise, the event count reported will be zero. It is

permissible and useful to set multiple request and response type bits in order to obtain various classes of off-core

response events. Although MSR_OFFCORE_RSPx allow an agent software to program numerous combinations that

meet the above guideline, not all combinations produce meaningful data.

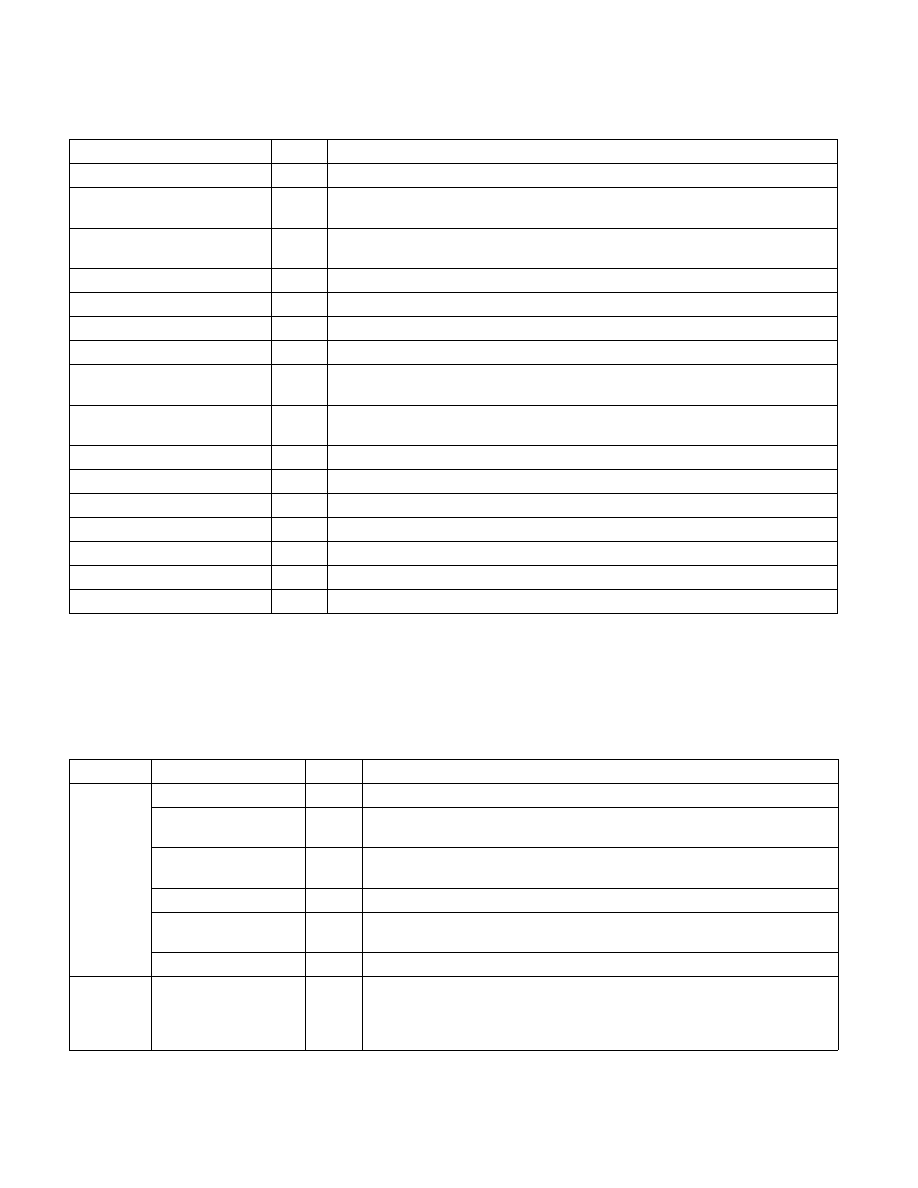

Table 18-21. MSR_OFFCORE_RSPx Request_Type Field Definition

Bit Name

Offset

Description

DEMAND_DATA_RD

0

(R/W) Counts cacheline read requests due to demand reads (excludes prefetches).

DEMAND_RFO

1

(R/W) Counts cacheline read for ownership (RFO) requests due to demand writes

(excludes prefetches).

DEMAND_CODE_RD

2

(R/W) Counts demand instruction cacheline and I-side prefetch requests that miss the

instruction cache.

COREWB

3

(R/W) Counts writeback transactions caused by L1 or L2 cache evictions.

PF_L2_DATA_RD

4

(R/W) Counts data cacheline reads generated by hardware L2 cache prefetcher.

PF_L2_RFO

5

(R/W) Counts reads for ownership (RFO) requests generated by L2 prefetcher.

Reserved

6

Reserved.

PARTIAL_READS

7

(R/W) Counts demand data partial reads, including data in uncacheable (UC) or

uncacheable (WC) write combining memory types.

PARTIAL_WRITES

8

(R/W) Counts partial writes, including uncacheable (UC), write through (WT) and write

protected (WP) memory type writes.

UC_CODE_READS

9

(R/W) Counts code reads in uncacheable (UC) memory region.

BUS_LOCKS

10

(R/W) Counts bus lock and split lock requests.

FULL_STREAMING_STORES

11

(R/W) Counts full cacheline writes due to streaming stores.

SW_PREFETCH

12

(R/W) Counts cacheline requests due to software prefetch instructions.

PF_L1_DATA_RD

13

(R/W) Counts data cacheline reads generated by hardware L1 data cache prefetcher.

PARTIAL_STREAMING_STORES

14

(R/W) Counts partial cacheline writes due to streaming stores.

ANY_REQUEST

15

(R/W) Counts requests to the uncore subsystem.

Table 18-22. MSR_OFFCORE_RSPx For L2 Miss and Outstanding Requests

Subtype

Bit Name

Offset

Description

L2_MISS

(Snoop Info)

Reserved

32:31

Reserved

L2_MISS.SNOOP_MISS_O

R_NO_SNOOP_NEEDED

33

(R/W). A true miss to this module, for which a snoop request missed the other

module or no snoop was performed/needed.

L2_MISS.HIT_OTHER_CO

RE_NO_FWD

34

(R/W) A snoop hit in the other processor module, but no data forwarding is

required.

Reserved

35

Reserved

L2_MISS.HITM_OTHER_C

ORE

36

(R/W) Counts the number of snoops hit in the other module or other core's L1

where modified copies were found.

L2_MISS.NON_DRAM

37

(R/W) Target was a non-DRAM system address. This includes MMIO transactions.

Outstanding

requests

1

OUTSTANDING

38

(R/W) Counts weighted cycles of outstanding offcore requests of the request type

specified in bits 15:0, from the time the XQ receives the request and any

response is received. Bits 37:16 must be set to 0. This bit is only available in

MSR_OFFCORE_RESP0.