Vol. 3B 18-27

PERFORMANCE MONITORING

To properly program this extra register, software must set at least one request type bit (Table 18-15) and a valid

response type pattern (Table 18-16, Table 18-17). Otherwise, the event count reported will be zero. It is permis-

sible and useful to set multiple request and response type bits in order to obtain various classes of off-core

response events. Although MSR_OFFCORE_RSPx allow an agent software to program numerous combinations that

meet the above guideline, not all combinations produce meaningful data.

To specify a complete offcore response filter, software must properly program bits in the request and response type

fields. A valid request type must have at least one bit set in the non-reserved bits of 15:0. A valid response type

must be a non-zero value of the following expression:

ANY | [(‘OR’ of Supplier Info Bits) & (‘OR’ of Snoop Info Bits)]

If “ANY” bit is set, the supplier and snoop info bits are ignored.

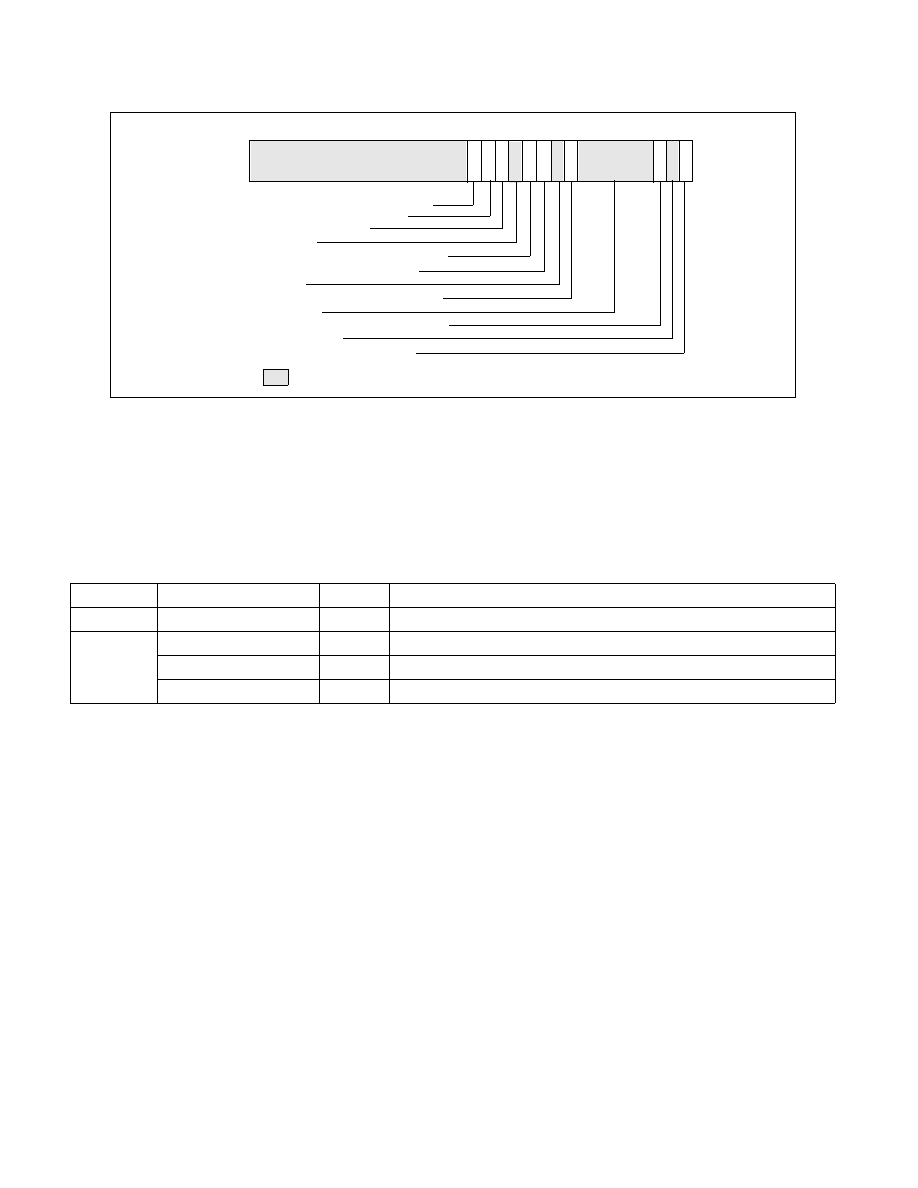

Figure 18-19. Response_Supplier and Snoop Info Fields for MSR_OFFCORE_RSPx

Table 18-16. MSR_OFFCORE_RSP_x Response Supplier Info Field Definition

Subtype

Bit Name

Offset

Description

Common

ANY_RESPONSE

16

(R/W). Catch all value for any response types.

Supplier Info Reserved

17

Reserved

L2_HIT

18

(R/W). Cache reference hit L2 in either M/E/S states.

Reserved

30:19

Reserved

RESPONSE TYPE — NON_DRAM (R/W)

RSPNS_SNOOP — HITM (R/W)

16

RESERVED

33

19

34

17

Reserved

63

18

20

31

21

22

32

35

36

37

RSPNS_SNOOP — SNOOP_HIT (R/W)

RSPNS_SNOOP — SNOOP_MISS (R/W)

RESERVED

RSPNS_SNOOP — SNOOP_NONE (R/W)

RESERVED

RSPNS_SUPPLIER — L2_HIT (R/W)

RESERVED

RSPNS_SUPPLIER — ANY (R/W)

RESET Value — 00000000_00000000H

38

AVG LATENCY — ENABLE AVG LATENCY(R/W)