Vol. 3B 18-9

PERFORMANCE MONITORING

Bit 21 (AnyThread) of IA32_PERFEVTSELx is supported in architectural performance monitoring version 3 for

processor core comprising of two or more logical processors. When set to 1, it enables counting the associated

event conditions (including matching the thread’s CPL with the OS/USR setting of IA32_PERFEVTSELx)

occurring across all logical processors sharing a processor core. When bit 21 is 0, the counter only increments

the associated event conditions (including matching the thread’s CPL with the OS/USR setting of

IA32_PERFEVTSELx) occurring in the logical processor which programmed the IA32_PERFEVTSELx MSR.

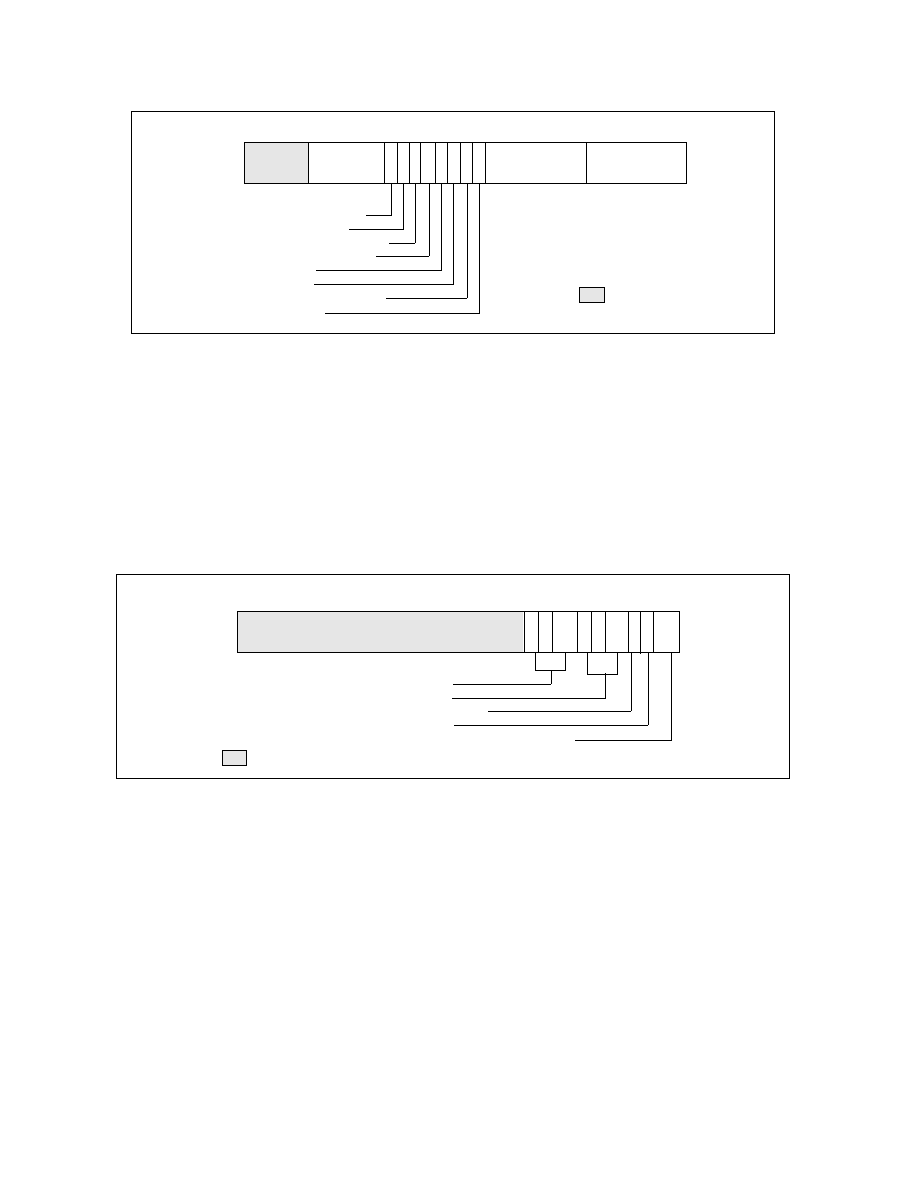

— Each fixed-function performance counter IA32_FIXED_CTRx (starting at MSR address 309H) is configured

by a 4-bit control block in the IA32_PERF_FIXED_CTR_CTRL MSR. The control block also allow thread-

specificity configuration using an AnyThread bit. The layout of IA32_PERF_FIXED_CTR_CTRL MSR is

shown.

Each control block for a fixed-function performance counter provides a AnyThread (bit position 2 + 4*N, N=

0, 1, etc.) bit. When set to 1, it enables counting the associated event conditions (including matching the

thread’s CPL with the ENABLE setting of the corresponding control block of IA32_PERF_FIXED_CTR_CTRL)

occurring across all logical processors sharing a processor core. When an AnyThread bit is 0 in

IA32_PERF_FIXED_CTR_CTRL, the corresponding fixed counter only increments the associated event

conditions occurring in the logical processor which programmed the IA32_PERF_FIXED_CTR_CTRL MSR.

•

The IA32_PERF_GLOBAL_CTRL, IA32_PERF_GLOBAL_STATUS, IA32_PERF_GLOBAL_OVF_CTRL MSRs provide

single-bit controls/status for each general-purpose and fixed-function performance counter. Figure 18-8 and

Figure 18-9 show the layout of these MSRs for N general-purpose performance counters (where N is reported

by CPUID.0AH:EAX[15:8]) and three fixed-function counters.

Note: The number of general-purpose performance monitoring counters (i.e. N in Figure 18-9) can vary across

processor generations within a processor family, across processor families, or could be different depending on

the configuration chosen at boot time in the BIOS regarding Intel Hyper Threading Technology, (e.g. N=2 for

45 nm Intel Atom processors; N =4 for processors based on the Nehalem microarchitecture; for processors

Figure 18-6. Layout of IA32_PERFEVTSELx MSRs Supporting Architectural Performance Monitoring Version 3

Figure 18-7. IA32_FIXED_CTR_CTRL MSR Supporting Architectural Performance Monitoring Version 3

31

INV—Invert counter mask

EN—Enable counters

INT—APIC interrupt enable

PC—Pin control

8 7

0

Event Select

E—Edge detect

OS—Operating system mode

USR—User Mode

Counter Mask

E

E

N

I

N

T

19

16

18

15

17

20

21

22

23

24

Reserved

I

N

V

P

C

U

S

R

O

S

Unit Mask (UMASK)

(CMASK)

63

ANY—Any Thread

A

N

Y

Cntr2 — Controls for IA32_FIXED_CTR2

Cntr1 — Controls for IA32_FIXED_CTR1

PMI — Enable PMI on overflow on IA32_FIXED_CTR0

AnyThread — AnyThread for IA32_FIXED_CTR0

8 7

0

ENABLE — IA32_FIXED_CTR0. 0: disable; 1: OS; 2: User; 3: All ring levels

E

N

P

M

I

11

3

12

1

Reserved

63

2

E

N

E

N

4

9

5

P

P

M

M

I

I

A

N

Y

A

N

Y

A

N

Y