18-4 Vol. 3B

PERFORMANCE MONITORING

•

Unit mask (UMASK) field (bits 8 through 15) — These bits qualify the condition that the selected event

logic unit detects. Valid UMASK values for each event logic unit are specific to the unit. For each architectural

performance event, its corresponding UMASK value defines a specific microarchitectural condition.

A pre-defined microarchitectural condition associated with an architectural event may not be applicable to a

given processor. The processor then reports only a subset of pre-defined architectural events. Pre-defined

architectural events are listed in Table 18-1; support for pre-defined architectural events is enumerated using

CPUID.0AH:EBX. Architectural performance events available in the initial implementation are listed in Table

19-1.

•

USR (user mode) flag (bit 16) — Specifies that the selected microarchitectural condition is counted when

the logical processor is operating at privilege levels 1, 2 or 3. This flag can be used with the OS flag.

•

OS (operating system mode) flag (bit 17) — Specifies that the selected microarchitectural condition is

counted when the logical processor is operating at privilege level 0. This flag can be used with the USR flag.

•

E (edge detect) flag (bit 18) — Enables (when set) edge detection of the selected microarchitectural

condition. The logical processor counts the number of deasserted to asserted transitions for any condition that

can be expressed by the other fields. The mechanism does not permit back-to-back assertions to be distin-

guished.

This mechanism allows software to measure not only the fraction of time spent in a particular state, but also the

average length of time spent in such a state (for example, the time spent waiting for an interrupt to be

serviced).

•

PC (pin control) flag (bit 19) — When set, the logical processor toggles the PMi pins and increments the

counter when performance-monitoring events occur; when clear, the processor toggles the PMi pins when the

counter overflows. The toggling of a pin is defined as assertion of the pin for a single bus clock followed by

deassertion.

•

INT (APIC interrupt enable) flag (bit 20) — When set, the logical processor generates an exception

through its local APIC on counter overflow.

•

EN (Enable Counters) Flag (bit 22) — When set, performance counting is enabled in the corresponding

performance-monitoring counter; when clear, the corresponding counter is disabled. The event logic unit for a

UMASK must be disabled by setting IA32_PERFEVTSELx[bit 22] = 0, before writing to IA32_PMCx.

•

INV (invert) flag (bit 23) — When set, inverts the counter-mask (CMASK) comparison, so that both greater

than or equal to and less than comparisons can be made (0: greater than or equal; 1: less than). Note if

counter-mask is programmed to zero, INV flag is ignored.

•

Counter mask (CMASK) field (bits 24 through 31) — When this field is not zero, a logical processor

compares this mask to the events count of the detected microarchitectural condition during a single cycle. If

the event count is greater than or equal to this mask, the counter is incremented by one. Otherwise the counter

is not incremented.

This mask is intended for software to characterize microarchitectural conditions that can count multiple

occurrences per cycle (for example, two or more instructions retired per clock; or bus queue occupations). If

the counter-mask field is 0, then the counter is incremented each cycle by the event count associated with

multiple occurrences.

18.2.1.2 Pre-defined Architectural Performance Events

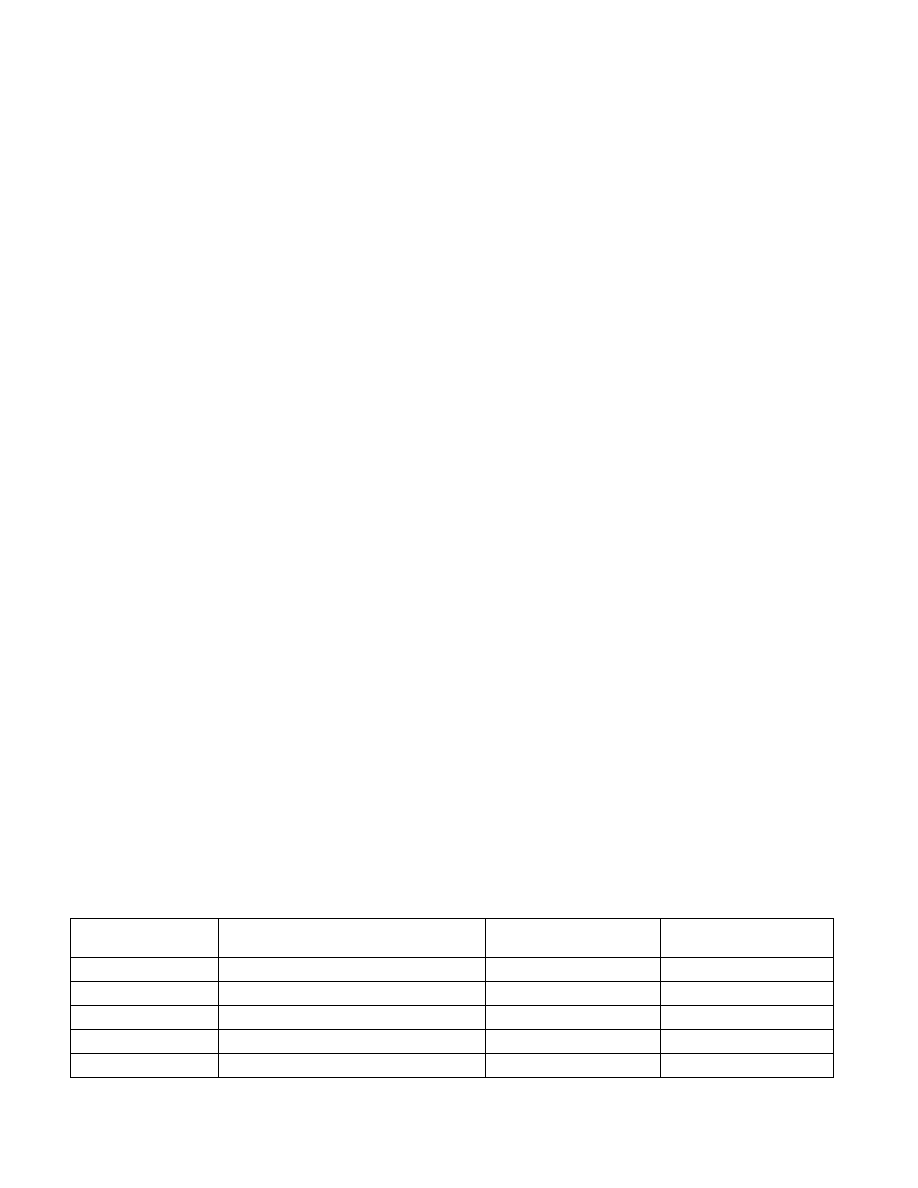

Table 18-1 lists architecturally defined events.

Table 18-1. UMask and Event Select Encodings for Pre-Defined Architectural Performance Events

Bit Position

CPUID.AH.EBX

Event Name

UMask

Event Select

0

UnHalted Core Cycles

00H

3CH

1

Instruction Retired

00H

C0H

2

UnHalted Reference Cycles

01H

3CH

3

LLC Reference

4FH

2EH

4

LLC Misses

41H

2EH