Vol. 3B 17-57

DEBUG, BRANCH PROFILE, TSC, AND RESOURCE MONITORING FEATURES

caches after a migration. In general, for best performance, minimize thread migration and COS migration across

processor logical threads and processor cores.

17.17.3.3 Cache Allocation Technology: Cache Mask Configuration

After determining the length of the capacity bitmasks (CBM) and number of COS supported using CPUID (see

Section 17.17.3.2), each COS needs to be programmed with a CBM to dictate its available cache via a write to the

corresponding IA32_resourceType_MASK_n register, where 'n' corresponds to a number within the supported

range of COS, i.e. the range between 0 and CPUID.(EAX=10H, ECX=ResID):EDX[15:0], inclusive, and

'resourceType' corresponds to a specific resource as enumerated by the set bits of CPUID.(EAX=10H,

ECX=0):EAX[31:1], for instance, ‘L2’ or ‘L3’ cache.

A hierarchy of MSRs is reserved for Cache Allocation Technology registers of the form

IA32_resourceType_MASK_n:

•

from 0C90H through 0D8FH (inclusive), providing support for multiple sub-ranges to support varying resource

types. The first supported resourceType is 'L3', corresponding to the L3 cache in a platform. The MSRs range

from 0C90H through 0D0FH (inclusive), enables support for up to 128 L3 CAT Classes of Service.

•

Within the same CAT range hierarchy, another set of registers is defined for resourceType 'L2', corresponding

to the L2 cache in a platform, and MSRs IA32_L2_MASK_n are defined for n=[0,63] at addresses 0D10H

through 0D4FH (inclusive).

Figure 17-34 and Figure 17-35 provide an overview of the relevant registers.

All CAT configuration registers can be accessed using the standard RDMSR / WRMSR instructions.

Note that once L3 or L2 CAT masks are configured, threads can be grouped into Classes of Service (COS) using the

IA32_PQR_ASSOC MSR as described in Section 17.17.3.4 (Class of Service (COS) to Cache Mask Association:

Common Across Allocation Features)

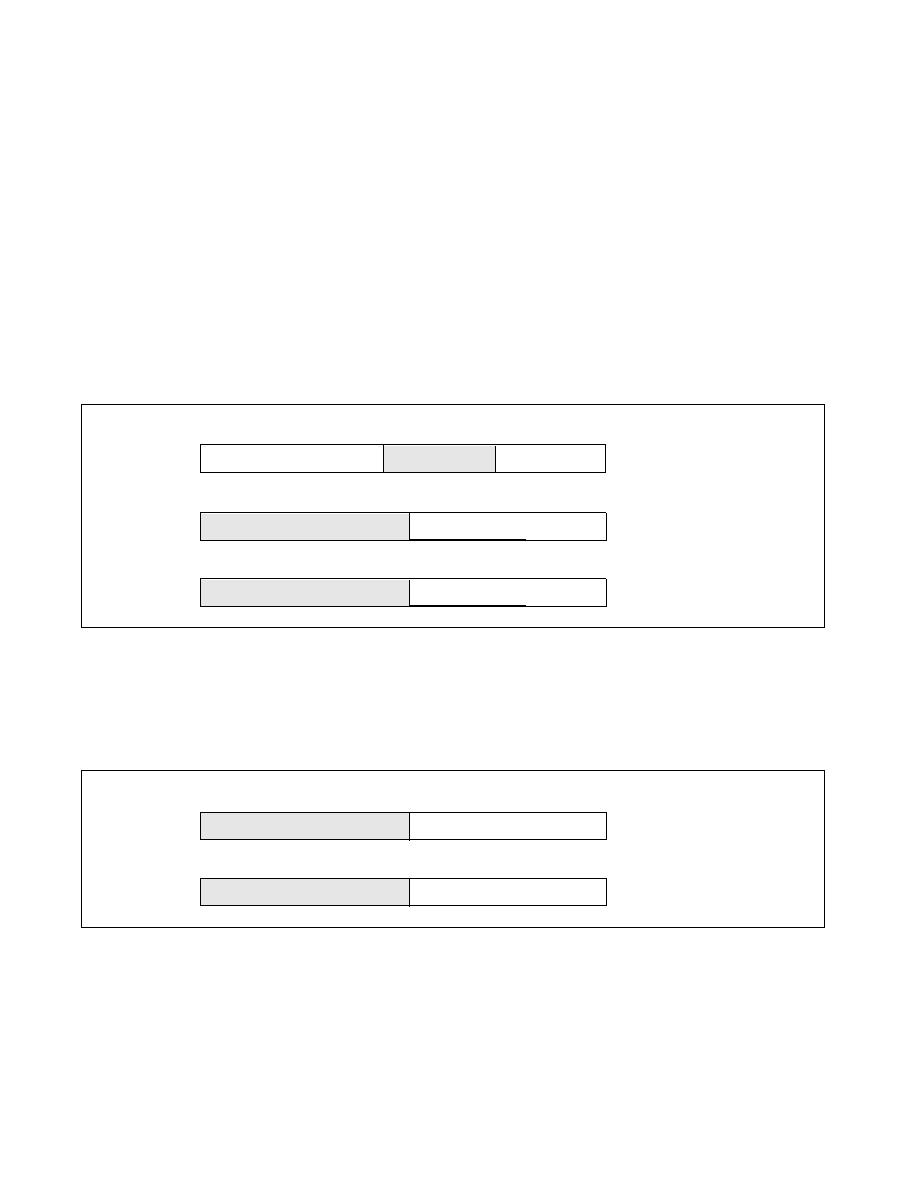

Figure 17-34. IA32_PQR_ASSOC, IA32_L3_MASK_n MSRs

Figure 17-35. IA32_L2_MASK_n MSRs

0

10

63

RMID

9

Reserved

IA32_PQR_ASSOC

IA32_L3_MASK_n

0

31

63

Reserved

IA32_L3_MASK_0

32

Bit_Mask

31

COS

....

0

31

63

Reserved

32

Bit_Mask

IA32_L2_MASK_n

0

31

63

Reserved

IA32_L2_MASK_0

32

Bit_Mask

....

0

31

63

Reserved

32

Bit_Mask