Vol. 3B 17-47

DEBUG, BRANCH PROFILE, TSC, AND RESOURCE MONITORING FEATURES

RMID may allow cache occupancy, memory bandwidth information or other monitoring data to be read back later

with monitoring event codes (retrieving data is discussed in a previous section).

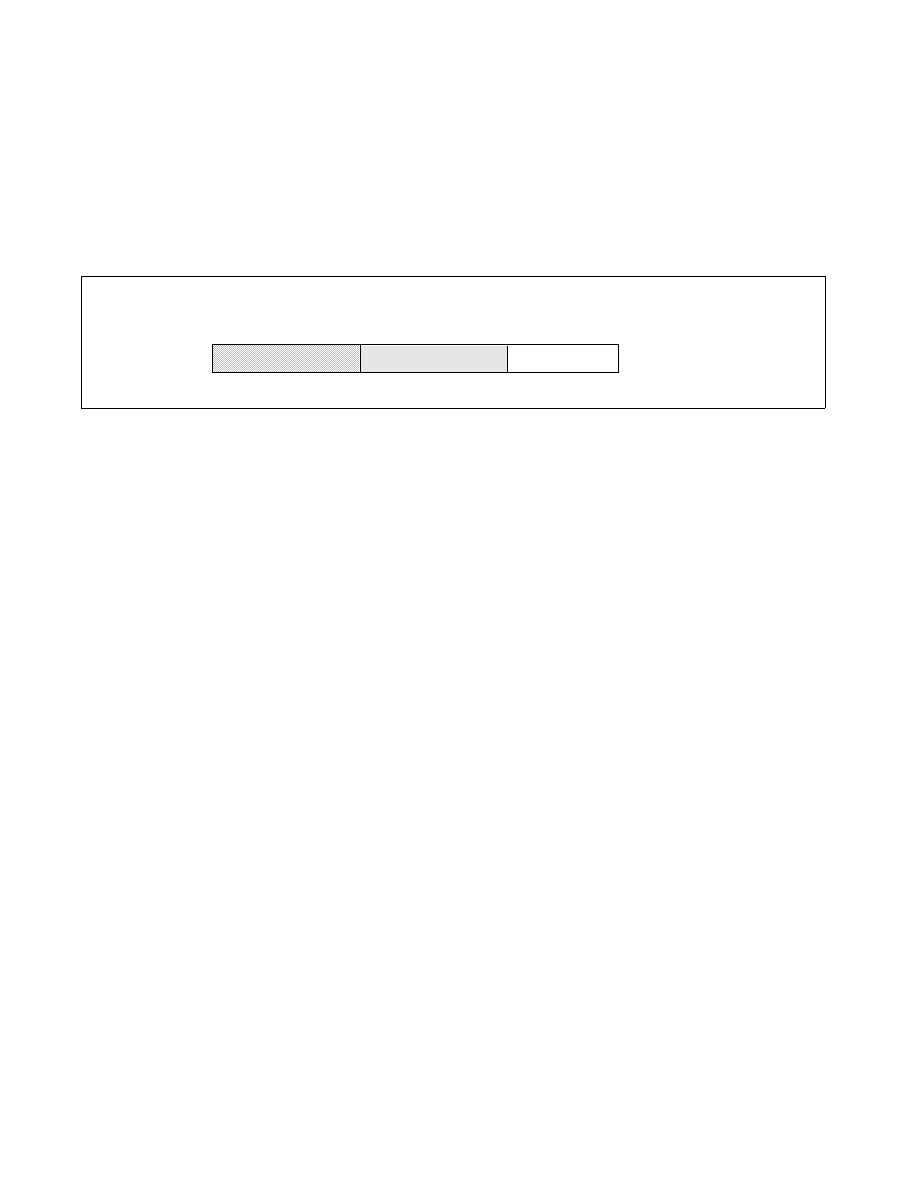

The association of an application thread with an RMID requires an OS to program the per-logical-processor MSR

IA32_PQR_ASSOC at context swap time (updates may also be made at any other arbitrary points during program

execution such as application phase changes). The IA32_PQR_ASSOC MSR specifies the active RMID that moni-

toring hardware will use to tag internal operations, such as L3 cache requests. The layout of the MSR is shown in

Figure 17-23. Software specifies the active RMID to monitor in the IA32_PQR_ASSOC.RMID field. The width of the

RMID field can vary from one implementation to another, and is derived from Ceil (LOG

2

( 1 + CPUID.(EAX=0FH,

ECX=0):EBX[31:0])). The value of IA32_PQR_ASSOC after power-on is 0.

In the initial implementation, the width of the RMID field is up to 10 bits wide, zero-referenced and fully encoded.

However, software must use CPUID to query the maximum RMID supported by the processor. If a value larger than

the maximum RMID is written to IA32_PQR_ASSOC.RMID, a #GP(0) fault will be generated.

RMIDs have a global scope within the physical package- if an RMID is assigned to one logical processor then the

same RMID can be used to read multiple thread attributes later (for example, L3 cache occupancy or external

bandwidth from the L3 to the next level of the cache hierarchy). In a multiple LLC platform the RMIDs are to be

reassigned by the OS or VMM scheduler when an application is migrated across LLCs.

Note that in a situation where Monitoring supports multiple resource types, some upper range of RMIDs (e.g. RMID

31) may only be supported by one resource type but not by another resource type.

17.16.7 Monitoring Resource Selection and Reporting Infrastructure

The reporting mechanism for Cache Monitoring Technology and other related features is architecturally exposed as

an MSR pair that can be programmed and read to measure various metrics such as the L3 cache occupancy (CMT)

and bandwidths (MBM) depending on the level of Monitoring support provided by the platform. Data is reported

back on a per-RMID basis. These events do not trigger based on event counts or trigger APIC interrupts (e.g. no

Performance Monitoring Interrupt occurs based on counts). Rather, they are used to sample counts explicitly.

The MSR pair for the shared resource monitoring features (CMT, MBM) is separate from and not shared with archi-

tectural Perfmon counters, meaning software can use these monitoring features simultaneously with the Perfmon

counters.

Access to the aggregated monitoring information is accomplished through the following programmable monitoring

MSRs:

•

IA32_QM_EVTSEL: This MSR provides a role similar to the event select MSRs for programmable performance

monitoring described in Chapter 18. The simplified layout of the MSR is shown in Figure 17-24. Bits

IA32_QM_EVTSEL.EvtID (bits 7:0) specify an event code of a supported resource type for hardware to report

monitored data associated with IA32_QM_EVTSEL.RMID (bits 41:32). Software can configure

IA32_QM_EVTSEL.RMID with any RMID that is active within the physical processor. The width of

IA32_QM_EVTSEL.RMID matches that of IA32_PQR_ASSOC.RMID. Supported event codes for the

IA32_QM_EVTSEL register are shown in Table 17-19. Note that valid event codes may not necessarily map

directly to the bit position used to enumerate support for the resource via CPUID.

Software can program an RMID / Event ID pair into the IA32_QM_EVTSEL MSR bit field to select an RMID to

read a particular counter for a given resource. The currently supported list of Monitoring Event IDs is discussed

in Section 17.16.5, which covers feature-specific details.

Figure 17-23. IA32_PQR_ASSOC MSR

0

10

63

Width of IA32_PQR_ASSOC.RMID field: Log

2

( CPUID.(EAX=0FH, ECX=0H).EBX[31:0] +1)

RMID

9

Reserved

IA32_PQR_ASSOC

Reserved for CLOS*

32 31

*See Section 17.15