17-46 Vol. 3B

DEBUG, BRANCH PROFILE, TSC, AND RESOURCE MONITORING FEATURES

17.16.5.1 Cache Monitoring Technology

On processors for which Cache Monitoring Technology supports the L3 cache occupancy event, CPUID.(EAX=0FH,

ECX=1H).EDX would return with only bit 0 set. The corresponding event ID can be looked up from Table 17-19. The

L3 occupancy data accumulated in IA32_QM_CTR can be converted to total occupancy (in bytes) by multiplying

with CPUID.(EAX=0FH, ECX=1H).EBX.

Event codes for Cache Monitoring Technology are discussed in the next section.

17.16.5.2 Memory Bandwidth Monitoring

On processors that monitoring supports Memory Bandwidth Monitoring using ResID=1 (L3), two additional bits will

be set in the vector at CPUID.(EAX=0FH, ECX=1H).EDX:

•

CPUID.(EAX=0FH, ECX=1H).EDX[bit 1]: indicates the L3 total external bandwidth monitoring event is

supported if set. This event monitors the L3 total external bandwidth to the next level of the cache hierarchy,

including all demand and prefetch misses from the L3 to the next hierarchy of the memory system. In most

platforms, this represents memory bandwidth.

•

CPUID.(EAX=0FH, ECX=1H).EDX[bit 2]: indicates L3 local memory bandwidth monitoring event is supported if

set. This event monitors the L3 external bandwidth satisfied by the local memory. In most platforms that

support this event, L3 requests are likely serviced by a memory system with non-uniform memory architecture.

This allows bandwidth to off-package memory resources to be tracked by subtracting total from local bandwidth

(for instance, bandwidth over QPI to a memory controller on another physical processor could be tracked by

subtraction).

The corresponding Event ID can be looked up from Table 17-19. The L3 bandwidth data accumulated in

IA32_QM_CTR can be converted to total bandwidth (in bytes) using CPUID.(EAX=0FH, ECX=1H).EBX.

Table 17-19. Monitoring Supported Event IDs

17.16.6 Monitoring Resource RMID Association

After Monitoring and sub-features has been enumerated, software can begin using the monitoring features. The

first step is to associate a given software thread (or multiple threads as part of an application, VM, group of appli-

cations or other abstraction) with an RMID.

Note that the process of associating an RMID with a given software thread is the same for all shared resource moni-

toring features (CMT, MBM), and a given RMID number has the same meaning from the viewpoint of any logical

processors in a package. Stated another way, a thread may be associated in a 1:1 mapping with an RMID, and that

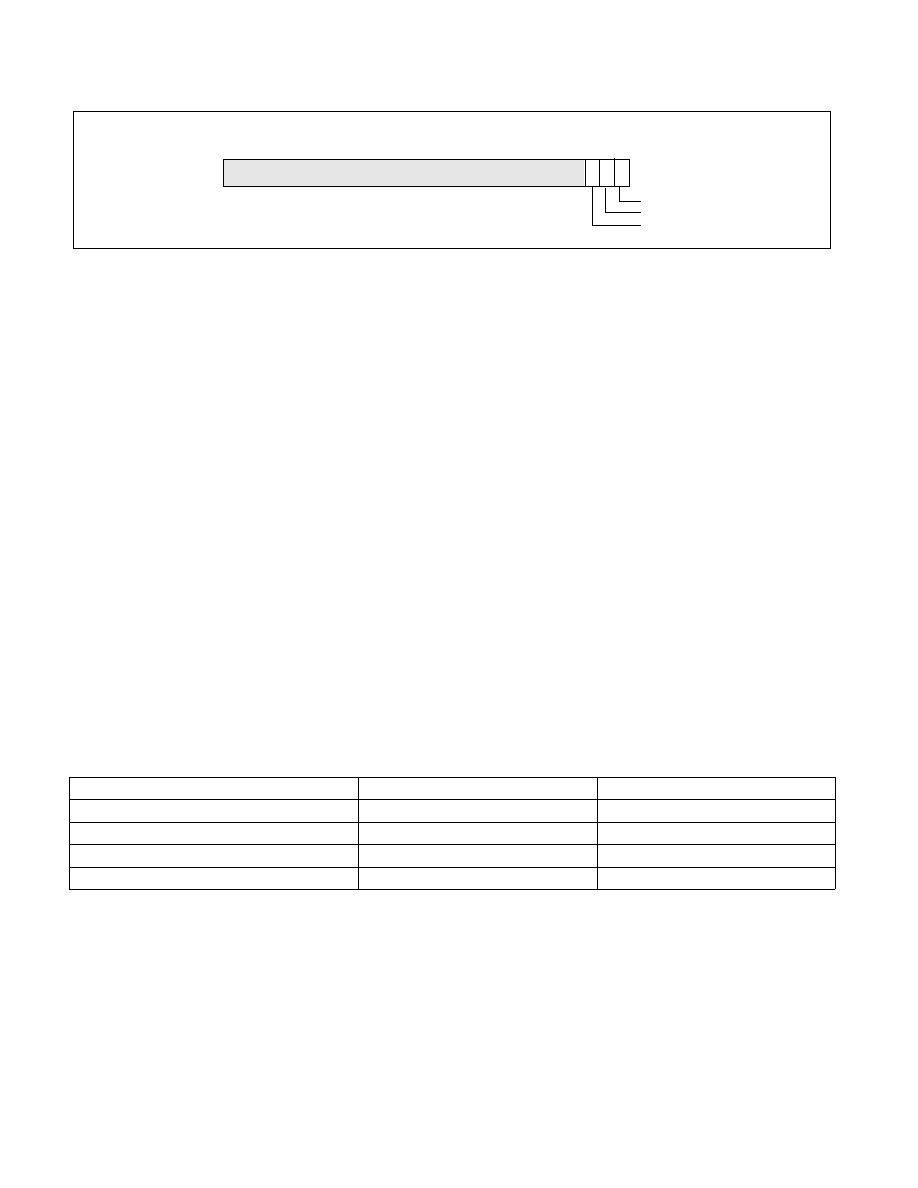

Figure 17-22. L3 Cache Monitoring Capability Enumeration Event Type Bit Vector (CPUID.(EAX=0FH, ECX=1H) )

Event Type

Event ID

Context

L3 Cache Occupancy

01H

Cache Monitoring Technology

L3 Total External Bandwidth

02H

MBM

L3 Local External Bandwidth

03H

MBM

Reserved

All other event codes

N/A

0

2

31

EDX

1

Reserved

EventTypeBitMask

3

L3 Occupancy

L3 Total BW

L3 Local BW