Vol. 3B 17-15

DEBUG, BRANCH PROFILE, TSC, AND RESOURCE MONITORING FEATURES

•

The BTS buffer is almost full and reaches the interrupt threshold.

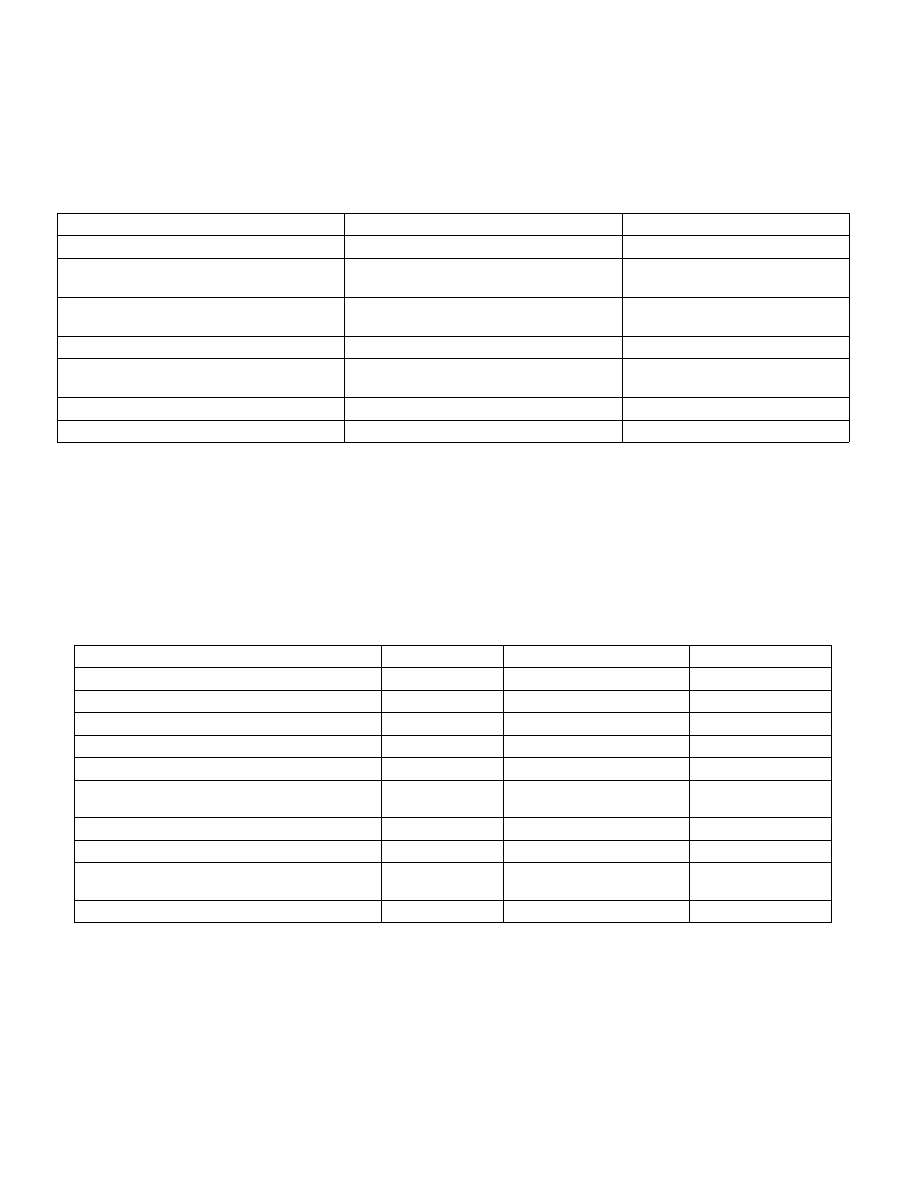

Table 17-3 compares the interaction of the processor with the PMI handler using the legacy versus streamlined

Freeza_Perfmon_On_PMI interface.

Table 17-3. Legacy and Streamlined Operation with Freeze_Perfmon_On_PMI = 1, Counter Overflowed

17.4.8 LBR

Stack

The last branch record stack and top-of-stack (TOS) pointer MSRs are supported across Intel 64 and IA-32

processor families. However, the number of MSRs in the LBR stack and the valid range of TOS pointer value can

vary between different processor families. Table 17-4 lists the LBR stack size and TOS pointer range for several

processor families according to the CPUID signatures of DisplayFamily_DisplayModel encoding (see CPUID instruc-

tion in Chapter 3 of Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 2A).

The last branch recording mechanism tracks not only branch instructions (like JMP, Jcc, LOOP and CALL instruc-

tions), but also other operations that cause a change in the instruction pointer (like external interrupts, traps and

faults). The branch recording mechanisms generally employs a set of MSRs, referred to as last branch record (LBR)

stack. The size and exact locations of the LBR stack are generally model-specific (see Chapter 35, “Model-Specific

Legacy Freeze_Perfmon_On_PMI

Streamlined Freeze_Perfmon_On_PMI

Comment

Processor freezes the counters on overflow

Processor freezes the counters on overflow

Unchanged

Processor clears IA32_PERF_GLOBAL_CTRL

Processor set

IA32_PERF_GLOBAL_STATUS.CTR_FTZ

Handler reads IA32_PERF_GLOBAL_STATUS

(0x38E) to examine which counter(s) overflowed

mask = RDMSR(0x38E)

Similar

Handler services the PMI

Handler services the PMI

Unchanged

Handler writes 1s to

IA32_PERF_GLOBAL_OVF_CTL (0x390)

Handler writes mask into

IA32_PERF_GLOBAL_OVF_RESET (0x390)

Processor clears IA32_PERF_GLOBAL_STATUS

Processor clears IA32_PERF_GLOBAL_STATUS Unchanged

Handler re-enables IA32_PERF_GLOBAL_CTRL

None

Reduced software overhead

Table 17-4. LBR Stack Size and TOS Pointer Range

DisplayFamily_DisplayModel

Size of LBR Stack

Component of an LBR Entry

Range of TOS Pointer

06_5CH, 06_5FH

32

FROM_IP, TO_IP

0 to 31

06_4EH, 06_5EH, 06_8EH, 06_9EH

32

FROM_IP, TO_IP, LBR_INFO

1

NOTES:

1. See Section 17.10.

0 to 31

06_3DH, 06_47H, 06_4FH, 06_56H

16

FROM_IP, TO_IP

0 to 15

06_3CH, 06_45H, 06_46H, 06_3FH

16

FROM_IP, TO_IP

0 to 15

06_2AH, 06_2DH, 06_3AH, 06_3EH

16

FROM_IP, TO_IP

0 to 15

06_1AH, 06_1EH, 06_1FH, 06_2EH, 06_25H,

06_2CH, 06_2FH

16

FROM_IP, TO_IP

0 to 15

06_17H, 06_1DH

4

FROM_IP, TO_IP

0 to 3

06_0FH

4

FROM_IP, TO_IP

0 to 3

06_37H, 06_4AH, 06_4CH, 06_4DH, 06_5AH,

06_5DH

8

FROM_IP, TO_IP

0 to 7

06_1CH, 06_26H, 06_27H, 06_35H, 06_36H

8

FROM_IP, TO_IP

0 to 7