16-28 Vol. 3B

INTERPRETING MACHINE-CHECK ERROR CODES

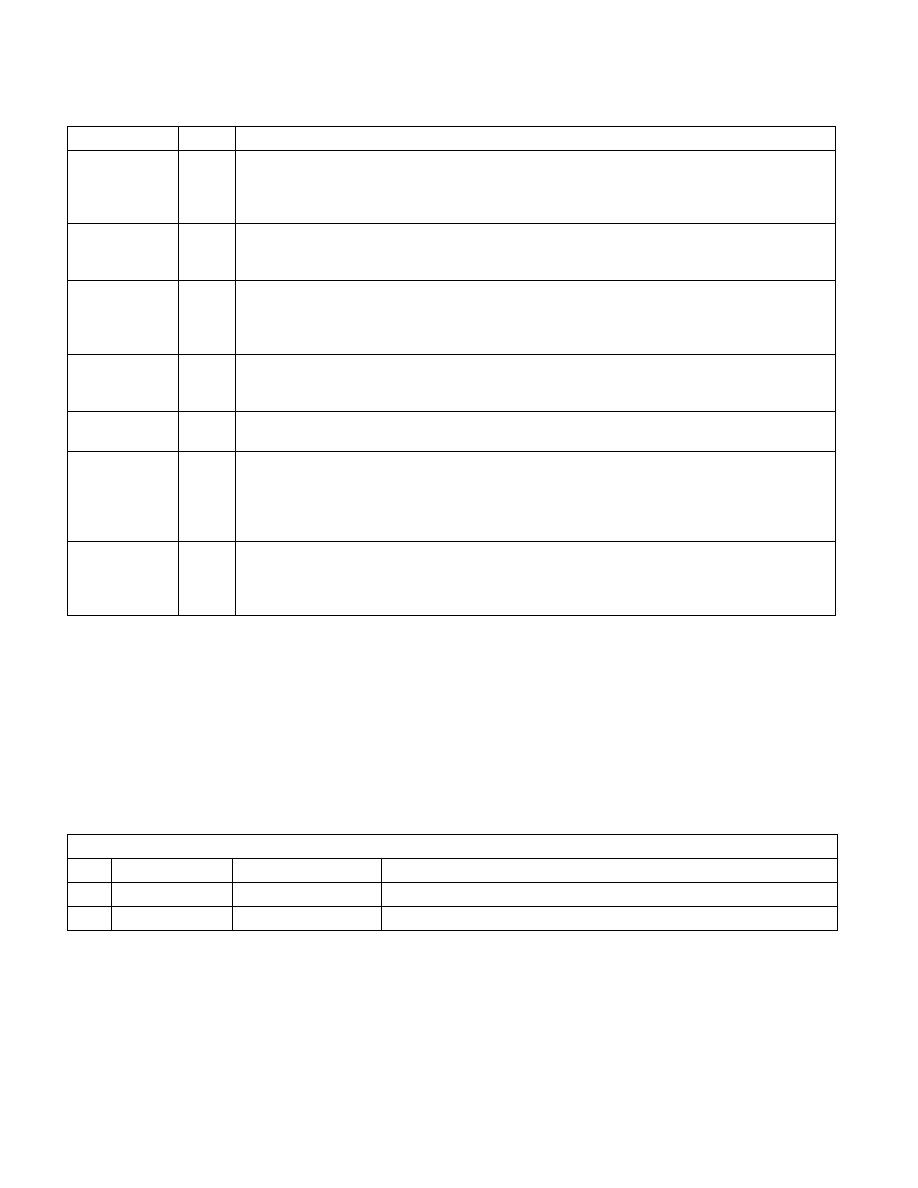

16.10.1.1 Processor Machine Check Status Register

MCA Error Code Definition

Intel Xeon processor MP 7100 series use compound MCA Error Codes for logging its CBC internal machine check

errors, L3 Errors, and Bus/Interconnect Errors. It defines additional Machine Check error types

(IA32_MC4_STATUS[15:0]) beyond those defined in Chapter 15. Table 16-33 lists these model-specific MCA error

codes. Error code details are specified in MC4_STATUS [31:16] (see Section 16.10.3), the “Model Specific Error

Code” field. The information in the “Other_Info” field (MC4_STATUS[56:32]) is common to the three processor

error types and contains a correctable event count and specifies the MC4_MISC register format.

PCC

57

Processor Context Corrupt flag indicates that the state of the processor might have been corrupted by

the error condition detected and that reliable restarting of the processor may not be possible. When

clear, this flag indicates that the error did not affect the processor's state. This bit will always be set for

MC errors which are not corrected.

ADDRV

58

MC_ADDR register valid flag indicates that the MC_ADDR register contains the address where the error

occurred. When clear, this flag indicates that the MC_ADDR register does not contain the address where

the error occurred. The MC_ADDR register should not be read if the ADDRV bit is clear.

MISCV

59

MC_MISC register valid flag indicates that the MC_MISC register contains additional

information regarding the error. When clear, this flag indicates that the MC_MISC register does not

contain additional information regarding the error. MC_MISC should not be read if the MISCV bit is not

set.

EN

60

Error enabled flag indicates that reporting of the machine check exception for this error was enabled by

the associated flag bit of the MC_CTL register. Note that correctable errors do not have associated

enable bits in the MC_CTL register so the EN bit should be clear when a correctable error is logged.

UC

61

Error uncorrected flag indicates that the processor did not correct the error condition. When clear, this

flag indicates that the processor was able to correct the event condition.

OVER

62

Machine check overflow flag indicates that a machine check error occurred while the results of a

previous error were still in the register bank (i.e., the VAL bit was already set in the

MC_STATUS register). The processor sets the OVER flag and software is responsible for clearing it.

Enabled errors are written over disabled errors, and uncorrected errors are written over corrected

events. Uncorrected errors are not written over previous valid uncorrected errors.

VAL

63

MC_STATUS register valid flag indicates that the information within the MC_STATUS register is valid.

When this flag is set, the processor follows the rules given for the OVER flag in the MC_STATUS register

when overwriting previously valid entries. The processor sets the VAL flag and software is responsible

for clearing it.

Table 16-33. Incremental MCA Error Code for Intel Xeon Processor MP 7100

Processor MCA_Error_Code (MC4_STATUS[15:0])

Type Error Code

Binary Encoding

Meaning

C

Internal Error

0000 0100 0000 0000 Internal Error Type Code

A

L3 Tag Error

0000 0001 0000 1011 L3 Tag Error Type Code

Table 16-32. MCi_STATUS Register Bit Definition (Contd.)

Bit Field Name

Bits

Description