16-30 Vol. 3B

INTERPRETING MACHINE-CHECK ERROR CODES

16.10.3 Processor Model Specific Error Code Field

16.10.3.1 MCA Error Type A: L3 Error

Note:

The Model Specific Error Code field in MC4_STATUS (bits 31:16).

16.10.3.2 Processor Model Specific Error Code Field Type B: Bus and Interconnect Error

Note:

The Model Specific Error Code field in MC4_STATUS (bits 31:16).

Exactly one of the bits defined in the preceding table will be set for a Bus and Interconnect Error. The Data ECC can

be correctable or uncorrectable (the MC4_STATUS.UC bit, of course, distinguishes between correctable and uncor-

rectable cases with the Other_Info field possibly providing the ECC Syndrome for correctable errors). All other

errors for this processor MCA Error Type are uncorrectable.

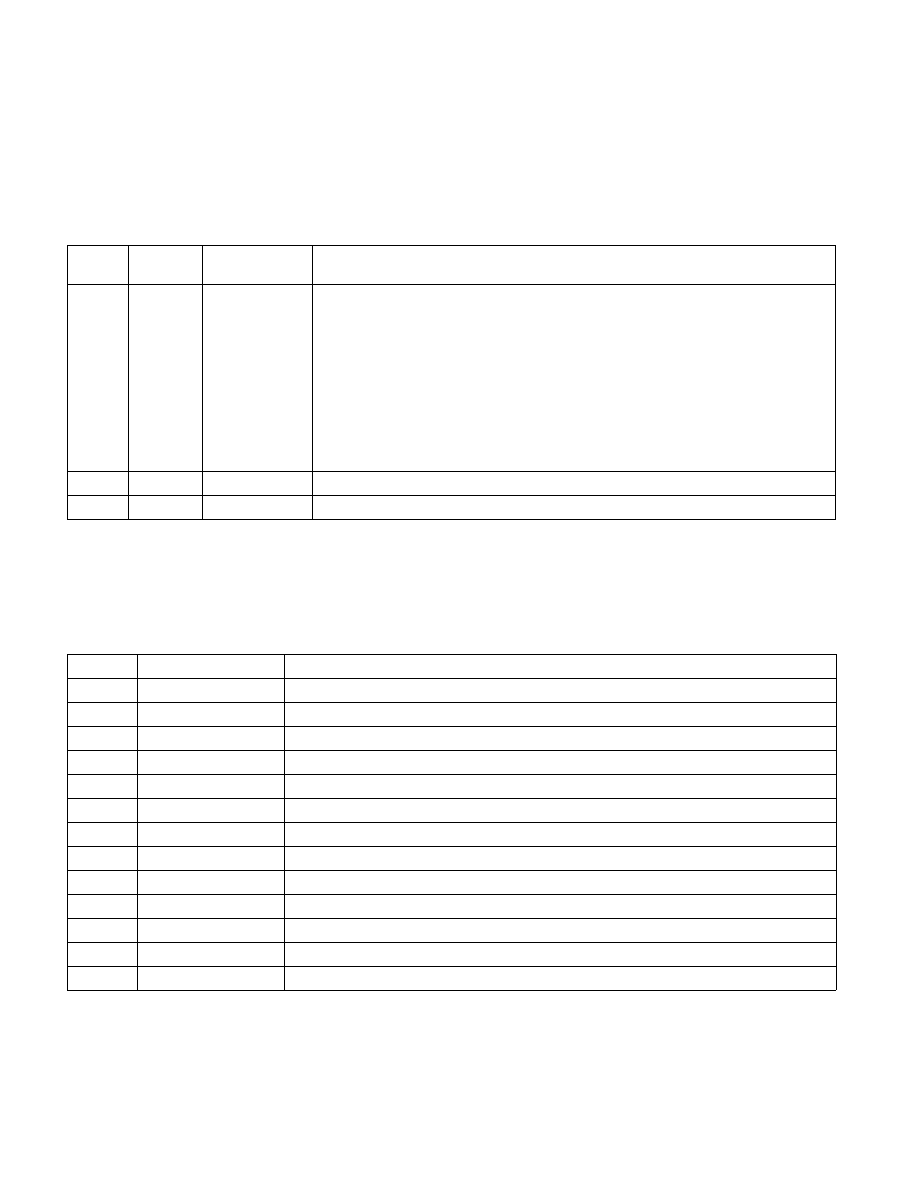

Table 16-35. Type A: L3 Error Codes

Bit

Num

Sub-Field

Name

Description

Legal Value(s)

18:16

L3 Error

Code

Describes the L3

error

encountered

000 - No error

001 - More than one way reporting a correctable event

010 - More than one way reporting an uncorrectable error

011 - More than one way reporting a tag hit

100 - No error

101 - One way reporting a correctable event

110 - One way reporting an uncorrectable error

111 - One or more ways reporting a correctable event while one or more ways are

reporting an uncorrectable error

20:19

–

Reserved 00

31:21

–

Fixed pattern

0010_0000_000

Table 16-36. Type B Bus and Interconnect Error Codes

Bit Num

Sub-Field Name

Description

16

FSB Request Parity

Parity error detected during FSB request phase

17

Core0 Addr Parity

Parity error detected on Core 0 request’s address field

18

Core1 Addr Parity

Parity error detected on Core 1 request’s address field

19

Reserved

20

FSB Response Parity

Parity error on FSB response field detected

21

FSB Data Parity

FSB data parity error on inbound data detected

22

Core0 Data Parity

Data parity error on data received from Core 0 detected

23

Core1 Data Parity

Data parity error on data received from Core 1 detected

24

IDS Parity

Detected an Enhanced Defer parity error (phase A or phase B)

25

FSB Inbound Data ECC

Data ECC event to error on inbound data (correctable or uncorrectable)

26

FSB Data Glitch

Pad logic detected a data strobe ‘glitch’ (or sequencing error)

27

FSB Address Glitch

Pad logic detected a request strobe ‘glitch’ (or sequencing error)

31:28

---

Reserved