Vol. 3B 16-21

INTERPRETING MACHINE-CHECK ERROR CODES

16.8

INCREMENTAL DECODING INFORMATION: PROCESSOR FAMILY WITH

CPUID DISPLAYFAMILY_DISPLAYMODEL SIGNATURE 06_4FH, MACHINE

ERROR CODES FOR MACHINE CHECK

Next Generation Intel Xeon processor E5 family is based on the Broadwell microarchitecture and can be identified

with CPUID DisplayFamily_DisplaySignature 06_4FH. Incremental error codes for internal machine check error

from PCU controller is reported in the register bank IA32_MC4, Table 16-20 in Section 16.6.1lists model-specific

fields to interpret error codes applicable to IA32_MC4_STATUS.

Incremental MC error codes related to the Intel QPI links are reported in the register banks IA32_MC5,

IA32_MC20, and IA32_MC21. Information listed in Table 16-21 of Section 16.6.1 covers QPI MC error codes.

16.8.1 Integrated Memory Controller Machine Check Errors

MC error codes associated with integrated memory controllers are reported in the MSRs IA32_MC9_STATUS-

IA32_MC16_STATUS. The supported error codes follow the architectural MCACOD definition type 1MMMCCCC (see

Chapter 15, “Machine-Check Architecture,”).

Table 16-26 lists model-specific error codes apply to IA32_MCi_STATUS, i = 9-16.

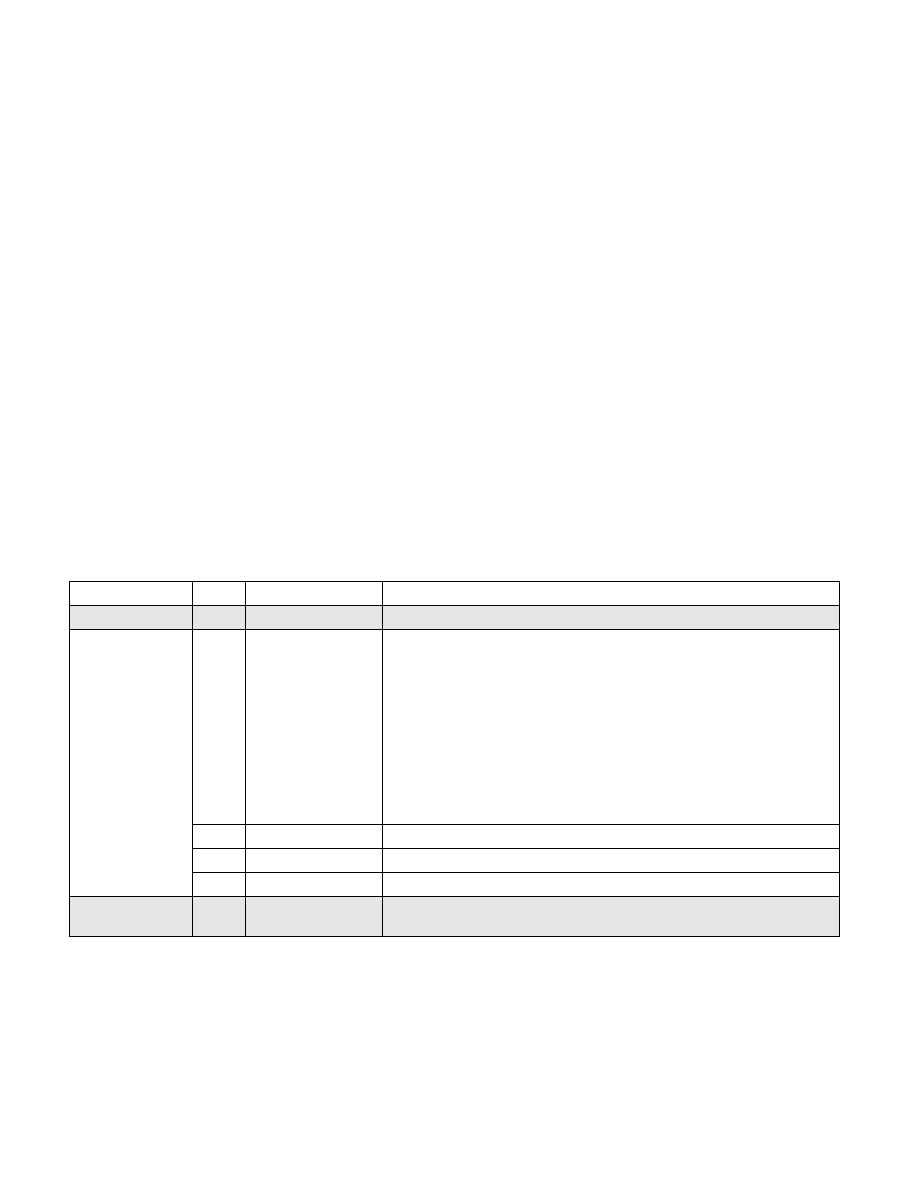

Table 16-26. Intel IMC MC Error Codes for IA32_MCi_STATUS (i= 9-16)

NOTES:

1. These fields are architecturally defined. Refer to Chapter 15, “Machine-Check Architecture,” for more information.

Type

Bit No. Bit Function

Bit Description

MCA error codes

1

NOTES:

1. These fields are architecturally defined. Refer to Chapter 15, “Machine-Check Architecture,” for more information.

0-15

MCACOD

Memory Controller error format: 0000 0000 1MMM CCCC

Model specific

errors

31:16

Reserved except for

the following

0001H - DDR3 address parity error

0002H - Uncorrected HA write data error

0004H - Uncorrected HA data byte enable error

0008H - Corrected patrol scrub error

0010H - Uncorrected patrol scrub error

0020H - Corrected spare error

0040H - Uncorrected spare error

0100H - iMC, write data buffer parity errors

0200H - DDR4 command address parity error

36-32

Other info

Reserved

37

Reserved

Reserved

56-38

See Chapter 15, “Machine-Check Architecture,”

Status register

validity indicators

1

57-63