Vol. 3B 16-17

INTERPRETING MACHINE-CHECK ERROR CODES

16.6.2 Intel QPI Machine Check Errors

MC error codes associated with the Intel QPI agents are reported in the MSRs IA32_MC5_STATUS,

IA32_MC20_STATUS, and IA32_MC21_STATUS. The supported error codes follow the architectural MCACOD defi-

nition type

1PPTRRRRIILL (see Chapter 15, “Machine-Check Architecture,”).

Table 16-21 lists model-specific fields to interpret error codes applicable to IA32_MC5_STATUS,

IA32_MC20_STATUS, and IA32_MC21_STATUS.

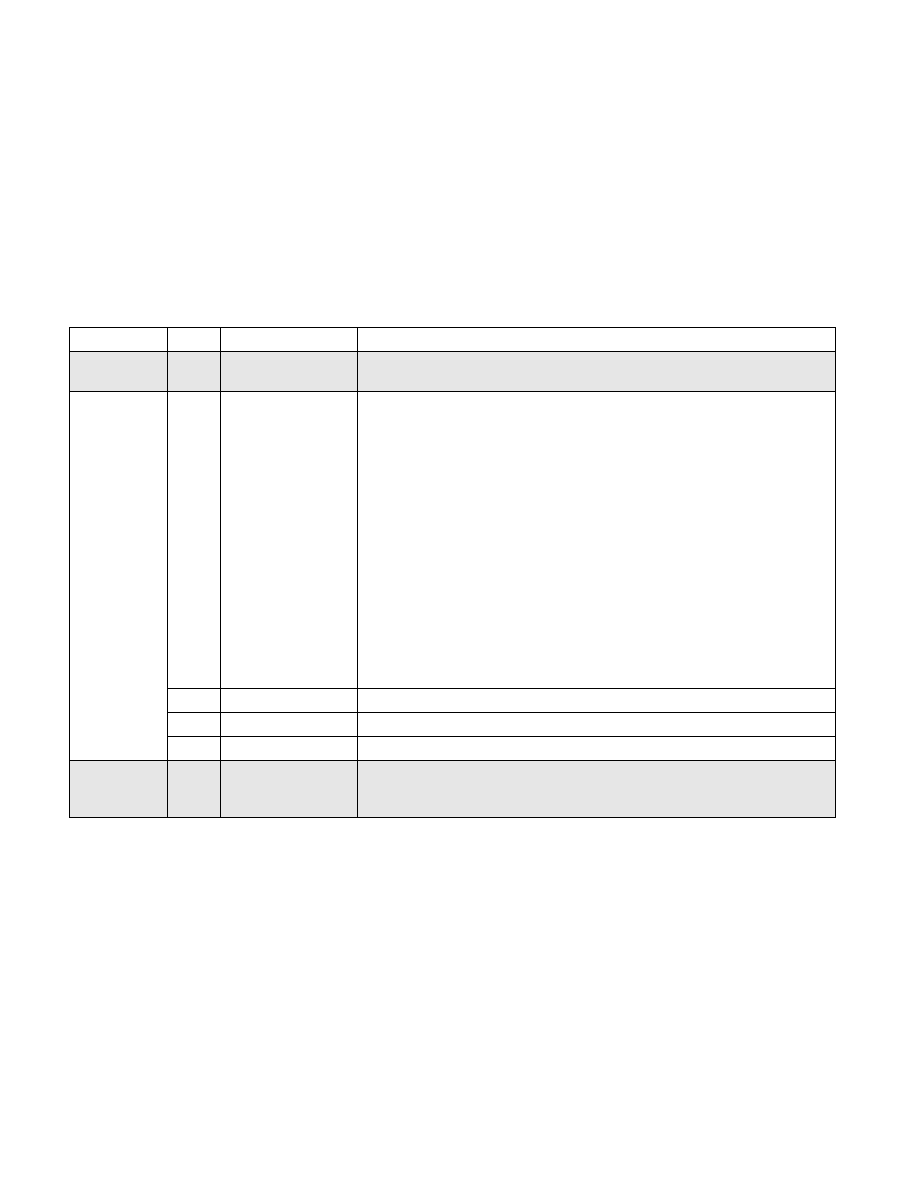

Table 16-21. Intel QPI MC Error Codes for IA32_MCi_STATUS (i = 5, 20, 21)

16.6.3 Integrated Memory Controller Machine Check Errors

MC error codes associated with integrated memory controllers are reported in the MSRs IA32_MC9_STATUS-

IA32_MC16_STATUS. The supported error codes follow the architectural MCACOD definition type 1MMMCCCC (see

Chapter 15, “Machine-Check Architecture,”).

MSR_ERROR_CONTROL.[bit 1] can enable additional information logging of the IMC. The additional error informa-

tion logged by the IMC is stored in IA32_MCi_STATUS and IA32_MCi_MISC; (i = 9-16).

2. The internal error codes may be model-specific.

Type

Bit No. Bit Function

Bit Description

MCA error

codes

1

NOTES:

1. These fields are architecturally defined. Refer to Chapter 15, “Machine-Check Architecture,” for more information.

0-15

MCACOD

Bus error format: 1PPTRRRRIILL

Model specific

errors

31-16

MSCOD

02h - Intel QPI physical layer detected drift buffer alarm.

03h - Intel QPI physical layer detected latency buffer rollover.

10h - Intel QPI link layer detected control error from R3QPI.

11h - Rx entered LLR abort state on CRC error.

12h - Unsupported or undefined packet.

13h - Intel QPI link layer control error.

15h - RBT used un-initialized value.

20h - Intel QPI physical layer detected a QPI in-band reset but aborted initialization

21h - Link failover data self-healing

22h - Phy detected in-band reset (no width change).

23h - Link failover clock failover

30h -Rx detected CRC error - successful LLR after Phy re-init.

31h -Rx detected CRC error - successful LLR without Phy re-init.

All other values are reserved.

37-32

Reserved

Reserved

52-38

Corrected Error Cnt

56-53

Reserved

Reserved

Status register

validity

indicators

1

57-63