Vol. 3B 16-15

INTERPRETING MACHINE-CHECK ERROR CODES

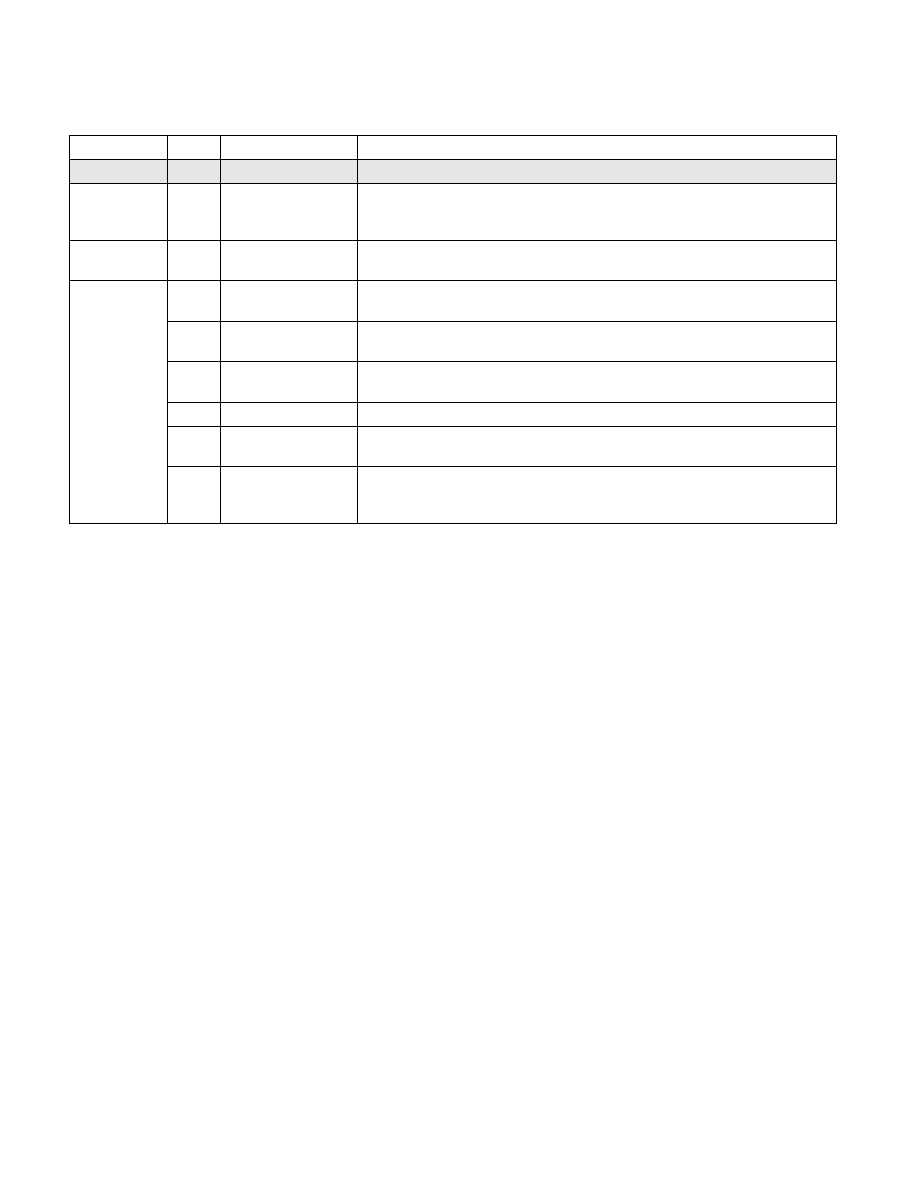

Table 16-19. Intel IMC MC Error Codes for IA32_MCi_MISC (i= 9-16)

16.6

INCREMENTAL DECODING INFORMATION: PROCESSOR FAMILY WITH

CPUID DISPLAYFAMILY_DISPLAYMODEL SIGNATURE 06_3FH, MACHINE

ERROR CODES FOR MACHINE CHECK

Intel Xeon processor E5 v3 family is based on the Haswell-E microarchitecture and can be identified with CPUID

DisplayFamily_DisplaySignature 06_3FH. Incremental error codes for internal machine check error from PCU

controller is reported in the register bank IA32_MC4, Table 16-20 lists model-specific fields to interpret error codes

applicable to IA32_MC4_STATUS. Incremental MC error codes related to the Intel QPI links are reported in the

register banks IA32_MC5, IA32_MC20, and IA32_MC21. Information listed in Table 16-21 for QPI MC error codes.

Incremental error codes for the memory controller unit is reported in the register banks IA32_MC9-IA32_MC16.

Table 16-22 lists model-specific error codes apply to IA32_MCi_STATUS, i = 9-16.

Type

Bit No. Bit Function

Bit Description

MCA addr info

1

NOTES:

1. These fields are architecturally defined. Refer to Chapter 15, “Machine-Check Architecture,” for more information.

0-8

See Chapter 15, “Machine-Check Architecture,”

Model specific

errors

13:9

If the error logged is MCWrDataPar error or MCWrBEPar error, this field is the WDB

ID that has the parity error. OR if the second error logged is a correctable read

error, MC logs the second error device in this field.

Model specific

errors

29-14

ErrMask_1stErrDev

When MSR_ERROR_CONTROL.[1] is set, allows the iMC to log first-device error bit

mask.

Model specific

errors

45-30

ErrMask_2ndErrDev

When MSR_ERROR_CONTROL.[1] is set, allows the iMC to log second-device error

bit mask.

50:46

FailRank_1stErrDev

When MSR_ERROR_CONTROL.[1] is set, allows the iMC to log first-device error

failing rank.

55:51

FailRank_2ndErrDev

When MSR_ERROR_CONTROL.[1] is set, allows the iMC to log second-device error

failing rank.

61:56

Reserved

62

Valid_1stErrDev

When MSR_ERROR_CONTROL.[1] is set, indicates the iMC has logged valid data

from a correctable error from memory read associated with first error device.

63

Valid_2ndErrDev

When MSR_ERROR_CONTROL.[1] is set, indicates the iMC has logged valid data due

to a second correctable error in a memory device. Use this information only after

there is valid first error info indicated by bit 62.