Vol. 3B 15-25

MACHINE-CHECK ARCHITECTURE

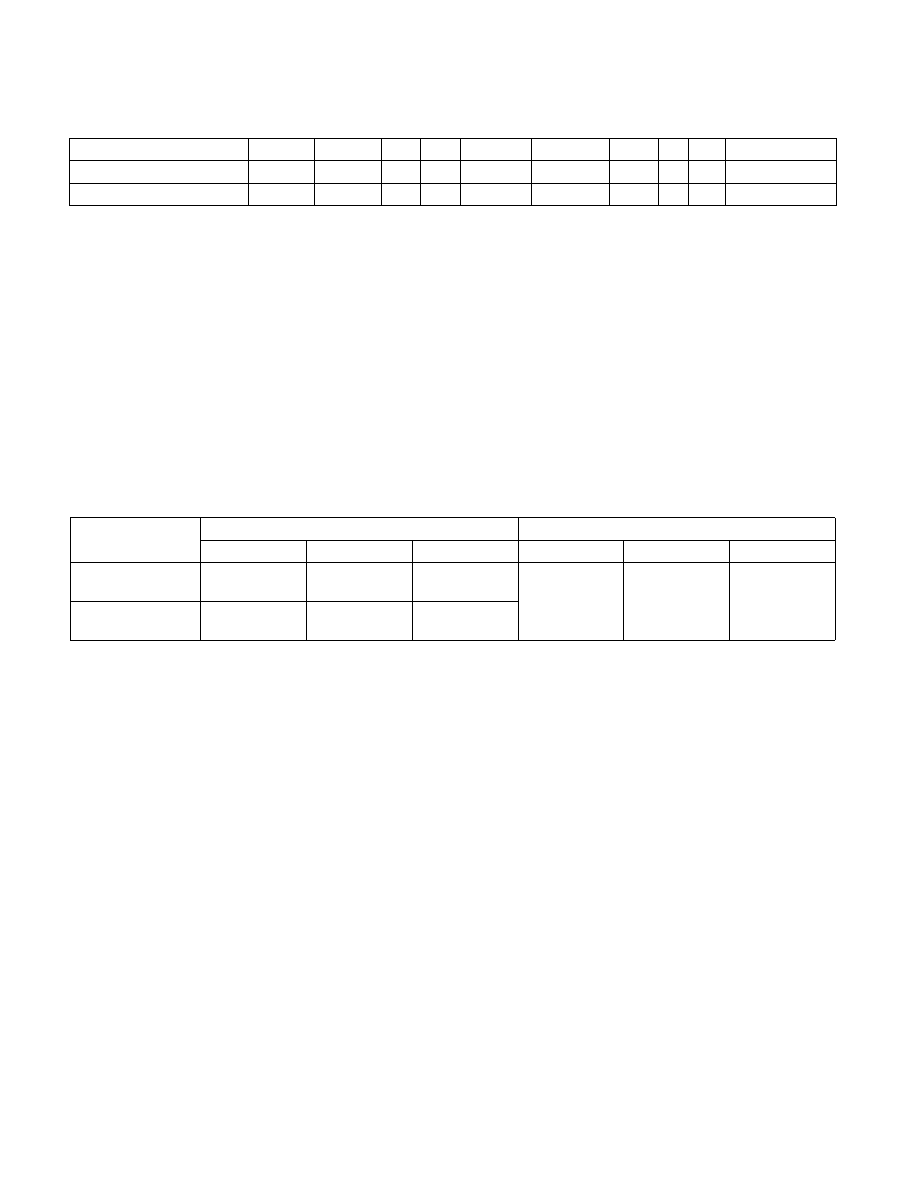

Table 15-19 lists values of relevant bit fields of IA32_MCi_STATUS for architecturally defined SRAR errors.

For both the data load and instruction fetch errors, the ADDRV and MISCV flags in the IA32_MCi_STATUS register

are set to indicate that the offending physical address information is available from the IA32_MCi_MISC and the

IA32_MCi_ADDR registers. For the memory scrubbing and L3 explicit writeback errors, the address mode in the

IA32_MCi_MISC register should be set as physical address mode (010b) and the address LSB information in the

IA32_MCi_MISC register should indicate the lowest valid address bit in the address information provided from the

IA32_MCi_ADDR register.

MCE signal is broadcast to all logical processors on the system on which the UCR errors are supported, except when

the processor supports LMCE and LMCE is enabled by system software (see Section 15.3.1.5). The

IA32_MCG_STATUS MSR allows system software to distinguish the affected logical processor of an SRAR error

amongst logical processors that observed SRAR via MCi_STATUS bank.

Table 15-20 shows the RIPV and EIPV flag indication in the IA32_MCG_STATUS register for the data load and

instruction fetch errors on both the reporting and non-reporting logical processors. The recoverable SRAR error

reported by a processor may be continuable, where the system software can interpret the context of continuable

as follows: the error was isolated, contained. If software can rectify the error condition in the current instruction

stream, the execution context on that logical processor can be continued without loss of information.

SRAR Error And Affected Logical Processors

The affected logical processor is the one that has detected and raised an SRAR error at the point of the consump-

tion in the execution flow. The affected logical processor should find the Data Load or the Instruction Fetch error

information in the IA32_MCi_STATUS register that is reporting the SRAR error.

Table 15-20 list the actionable scenarios that system software can respond to an SRAR error on an affected logical

processor according to RIPV and EIPV values:

•

Recoverable-Continuable SRAR Error (RIPV=1, EIPV=1):

For Recoverable-Continuable SRAR errors, the affected logical processor should find that both the

IA32_MCG_STATUS.RIPV and the IA32_MCG_STATUS.EIPV flags are set, indicating that system software may

be able to restart execution from the interrupted context if it is able to rectify the error condition. If system

software cannot rectify the error condition then it must treat the error as a recoverable error where restarting

execution with the interrupted context is not possible. Restarting without rectifying the error condition will

result in most cases with another SRAR error on the same instruction.

•

Recoverable-not-continuable SRAR Error (RIPV=0, EIPV=x):

For Recoverable-not-continuable errors, the affected logical processor should find that either

— IA32_MCG_STATUS.RIPV= 0, IA32_MCG_STATUS.EIPV=1, or

— IA32_MCG_STATUS.RIPV= 0, IA32_MCG_STATUS.EIPV=0.

Table 15-19. IA32_MCi_STATUS Values for SRAR Errors

SRAR Error

Valid

OVER

UC

EN

MISCV

ADDRV

PCC

S

AR

MCACOD

Data Load

1

0

1

1

1

1

0

1

1

134H

Instruction Fetch

1

0

1

1

1

1

0

1

1

150H

Table 15-20. IA32_MCG_STATUS Flag Indication for SRAR Errors

SRAR Type

Affected Logical Processor

Non-Affected Logical Processors

RIPV

EIPV

Continuable

RIPV

EIPV

Continuable

Recoverable-

continuable

1

1

Yes

1

NOTES:

1. see the definition of the context of “continuable” above and additional detail below.

1

0

Yes

Recoverable-not-

continuable

0

x

No